Testing method for chip synchronous clock and chip capable of synchronously testing clock function

A technology of synchronous clock and synchronous testing, applied in the direction of semiconductor/solid-state device testing/measurement, etc., can solve the problems of affecting the test results, difficulty in chip design, and inability to cross the delay time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The invention provides a chip testing method, which can avoid problems caused by asynchronous effects and improve the accuracy of chip testing.

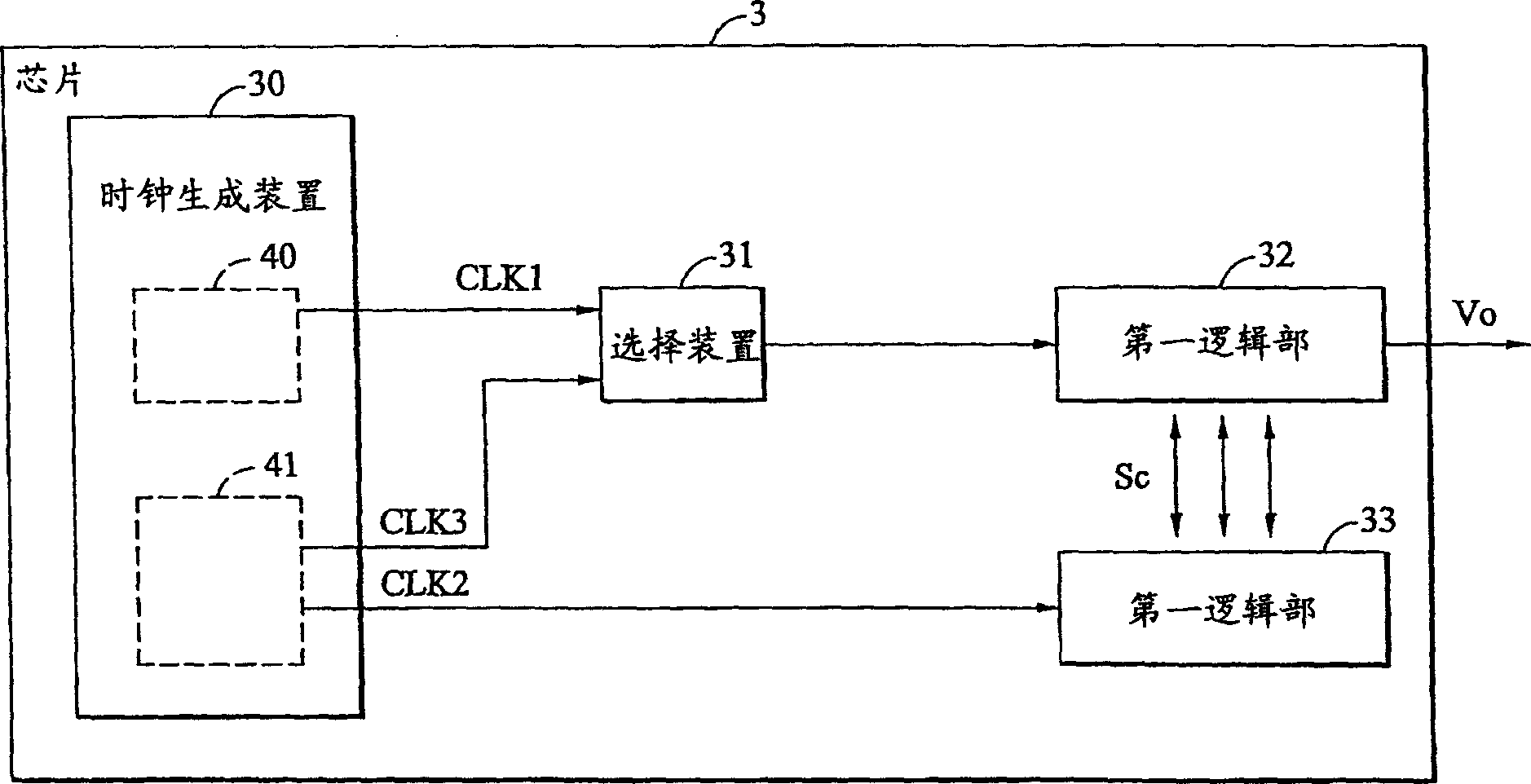

[0023] image 3 A chip to which the chip testing method of the present invention is applied is shown. Wherein, the chip 3 includes a clock generating device 30 , a selecting device 31 , a first logic part 32 and a second logic part 33 . During normal operation, the first logic part 32 is driven by the first clock signal CLK1, the second logic part 33 is driven by the second clock signal CLK2, and the operating frequency of the first clock CLK1 is higher than that of the second clock CLK2 and is not Integer multiples of the working frequency of the second clock signal CLK2. The clock generating device 30 includes a first clock generating device 40 and a second clock generating device 41; the first clock generating device 40 is used to generate the first clock signal CLK1, and the second clock generating device 41 is used to g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com