Coupling semiconductor testing device and interface circuit of the semiconductor device to be tested

A technology of interface circuit and test device, which is applied in the field of interface circuit, can solve the problems of inability to test, poor resolution accuracy of output voltage, and inability of tester to test correctly, so as to achieve the effect of reducing test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

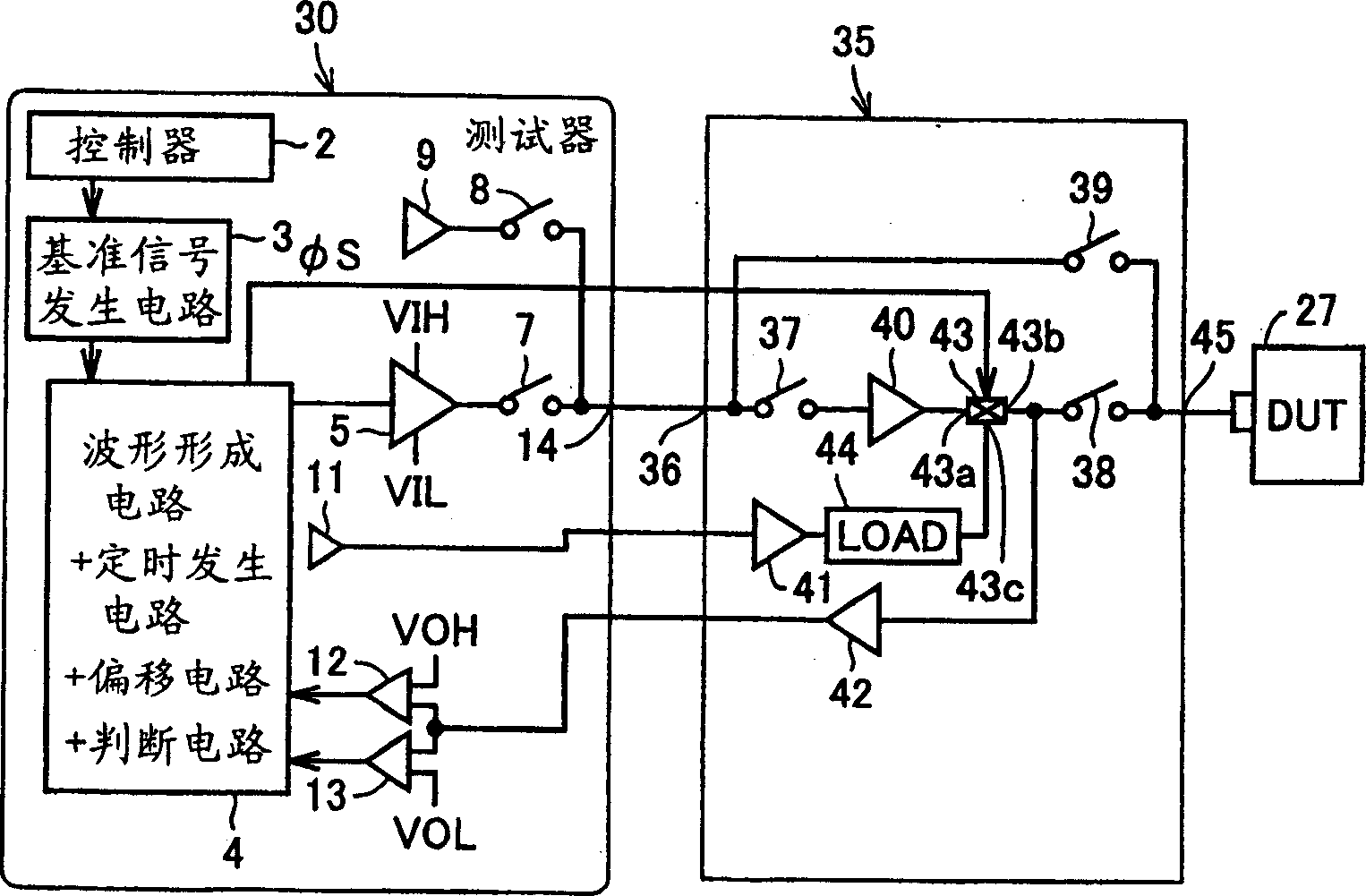

[0027] figure 1 It is a circuit block diagram showing main parts of the semiconductor test system according to the first embodiment of the present invention. figure 1 In this semiconductor test system, a tester 1 and an interface circuit 20 are provided. The tester 1 includes a controller 2, a reference signal generating circuit 3, a test circuit 4, an output buffer 5, a high-speed changeover switch 6, switches 7, 8, a current measuring unit 9, a load circuit (LOAD) 10, and a power supply 11 for the load circuit. , comparators 12, 13, and external plug 14. figure 1 Only one external plug 14 of the tester 1 and its corresponding part are shown in . In practice, a plurality of external plugs 14 are provided.

[0028] The controller 2 outputs various control signals at predetermined timings to control the entire tester 1 . The reference signal generating circuit 3 is controlled by the controller 2, and outputs a reference signal. The test circuit 4 includes a waveform forming...

Embodiment 2

[0045] figure 2 It is a circuit block diagram showing main parts of the semiconductor test system according to the second embodiment of the present invention. figure 2 In this semiconductor test system, a tester 30 and an interface circuit 35 are provided. Tester 30 is from figure 1 The tester removes the high-speed switch 6 and the load circuit 10. The output node of the output buffer 5 is supplied to the external plug 14 via the switch 7 , and the switching signal ΦS generated in the test circuit 4 is directly supplied to the interface circuit 35 . The load circuit power supply 11 and the comparators 12 and 13 are directly connected to the interface circuit 35 . figure 2 Only one external plug 14 of the tester 30 and its corresponding part are shown in . Actually, a plurality of external plugs 14 are provided.

[0046] The interface circuit 35 includes an input terminal 36 , switches 37 to 39 , buffers 40 to 42 , a high-speed changeover switch 43 , a load circuit 44 ,...

change example 1

[0060] Hereinafter, various modification examples will be described. Figure 5 The semiconductor test system has a tester 50 and an interface circuit 51 . Tester 50 is a combination of figure 1 of tester 1 and figure 2 The tester 30, the interface circuit 51 is a combination of the figure 1 The interface circuit 20 and figure 2 The interface circuit 35. This modification 1 can obtain both effects of the first and second embodiments.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com