Dynamic power control in integrated circuit

A power control, integrated circuit technology, applied in data processing power supply, electrical digital data processing, instruments, etc., can solve problems such as unsatisfactory, energy consumption, unpredictable delay time, etc., to achieve simplified structure and testing, power saving , the effect of saving power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

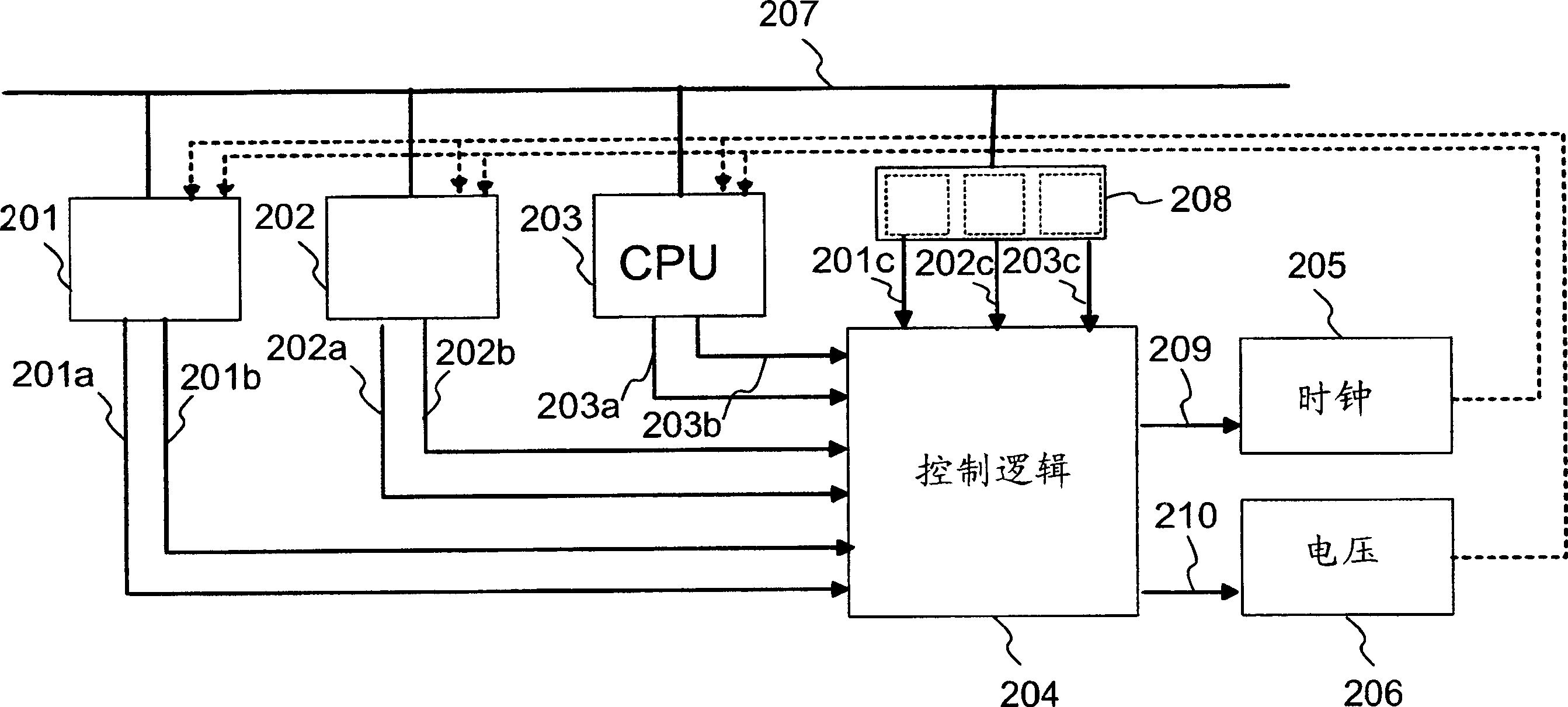

[0029] figure 2 A system preferably implemented on a single ASIC circuit is shown, comprising several hardware units 201-203, power control logic 204, and clock frequency and operating voltage control units 205 and 206. The hardware units 201 - 203 and the power control logic 204 are connected for communication via a bus 207 .

[0030] Each individual hardware unit 201 - 203 is capable of generating a first status signal 201 a - 203 a and a second status signal 201 b - 203 b which are communicated to the power control logic 204 according to the invention.

[0031] Also, the request signals 201c-203c are communicated to the power control logic 204, and the information is transferred from the power control mode register 208 to the power control logic 204. The power control mode register 208 contains information for each hardware unit 201-203 about the clock frequency and / or operating voltage to be generated for the individual hardware unit in power down mode. In other words, e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com