Wafer level packaging method and packaging structure

A wafer-level packaging and wafer technology, which is applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., to achieve the effect of simplifying the packaging method, avoiding long electroplating time, and taking into account electroplating efficiency and electroplating yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

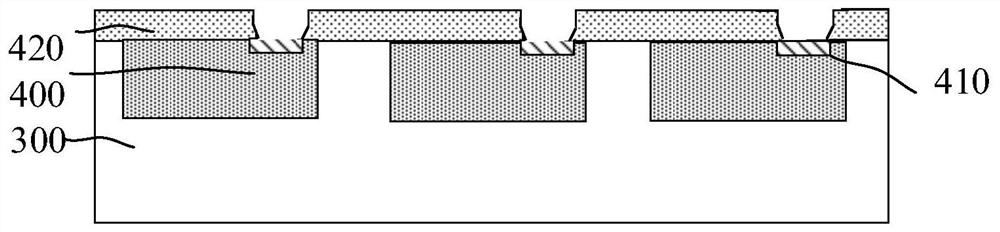

[0109] refer to Figure 9 , and the difference from the first embodiment is that a fourth pad 16 is formed on the other side of the first wafer 300 away from the second chip. During the electroplating process, a second conductive pad 16 is formed on the fourth pad 16 . Bump 80.

[0110] The exposed area of the fourth pad is 5-200 square microns. Within this range, the pad can be in sufficient contact with the electroplating solution to avoid insufficient contact between the pad and the electroplating solution and affect the conductive bumps and pads. For example, the contact area is too small to affect the resistance, or the inability to contact causes poor electrical contact.

[0111] Circuits are also formed in the first wafer 300, and the circuits are connected to the fourth pads through wiring layers or plugs, and the second conductive bumps 80 shown are used to connect external circuits. Alternatively, there is a TSV structure in the first wafer 300 as shown, the firs...

Embodiment 3

[0113] refer to Figure 10 , in the above embodiments of the present invention, the first chip is only bonded on one side of the first wafer, that is, the top surface. In the fifth embodiment of the present invention, it may be on the front side of the first wafer The first chip is bonded, the back side is also bonded to the first chip, a first gap is formed between the second pad on the first chip and the first pad on the front side of the first wafer, and the first pad on the back side of the first chip A first gap is formed between the pad and the fourth pad on the back of the first wafer. During the electroplating process, the first chip and the first wafer on the front side and the first chip on the back side and the first wafer are simultaneously formed. Conductive bumps 310 are formed therebetween. The electroplating process formed by the conductive bumps 310 on the front and the back can be performed simultaneously or separately; the first die bonding process on the f...

Embodiment 4

[0116] refer to Figure 11 In the sixth embodiment, a fifth pad 220 is formed on the other side of the second chip 200. After the second chip 200 is bonded on the first wafer, a third bonding pad 220 can be bonded on the second chip 30. The chip 501 can be bonded by a photolithographic bonding material, such as dry film; the third chip 501 includes a sixth pad 510, and a second gap is formed between the fifth pad and the sixth pad ; A third conductive bump 312 is formed in the second void by an electroplating process.

[0117] The fifth pad 220 and the second pad 210 are electrically connected through an interconnection structure. In this embodiment, the interconnection structure shown is a plug. In other embodiments, the interconnect structures shown may also be plugs and interconnect lines or pads.

[0118] The process of forming the third conductive bumps 312 may be the same as the forming process of forming the first conductive bumps 310 .

[0119] In this embodiment, t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| area | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com