On-chip super-large-scale power supply network parallel simulation method based on spectrogram rarefaction

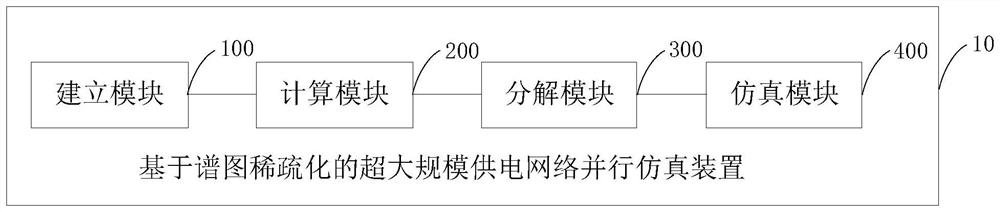

A power supply network, ultra-large-scale technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of low matrix parallel efficiency, and achieve the effects of high parallel efficiency, low memory consumption, and fast convergence speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Embodiments of the present application are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals denote the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary, and are intended to explain the present application, and should not be construed as limiting the present application.

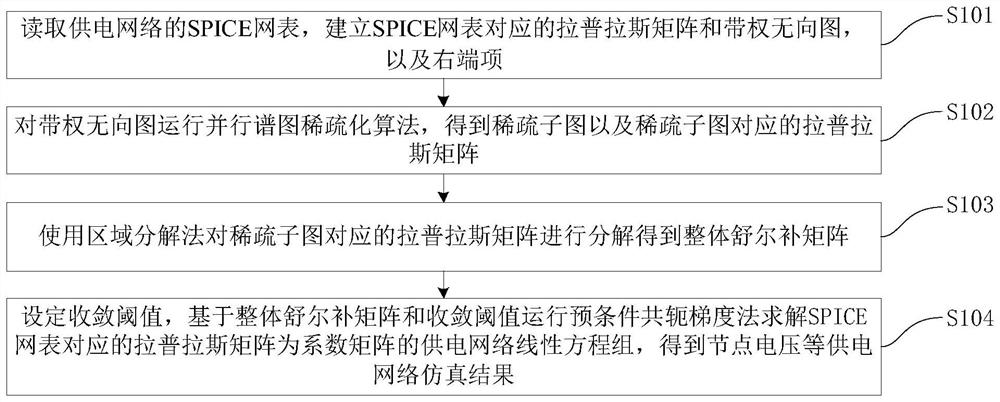

[0041] figure 1 It is a flow chart of a parallel simulation method for a very large-scale power supply network based on spectral graph sparsification provided according to an embodiment of the present application.

[0042] Such as figure 1 As shown, the parallel simulation method of ultra-large-scale power supply network based on spectral graph sparsification includes the following steps:

[0043] In step S101, the SPICE netlist of the power supply network is read, and the Laplacian matrix and weighted undirected graph cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com