Heterojunction cell and preparation method thereof

A heterojunction cell, broadband technology, applied in circuits, photovoltaic power generation, electrical components, etc., to achieve good anti-reflection performance, improve contact performance, and improve short-circuit current effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

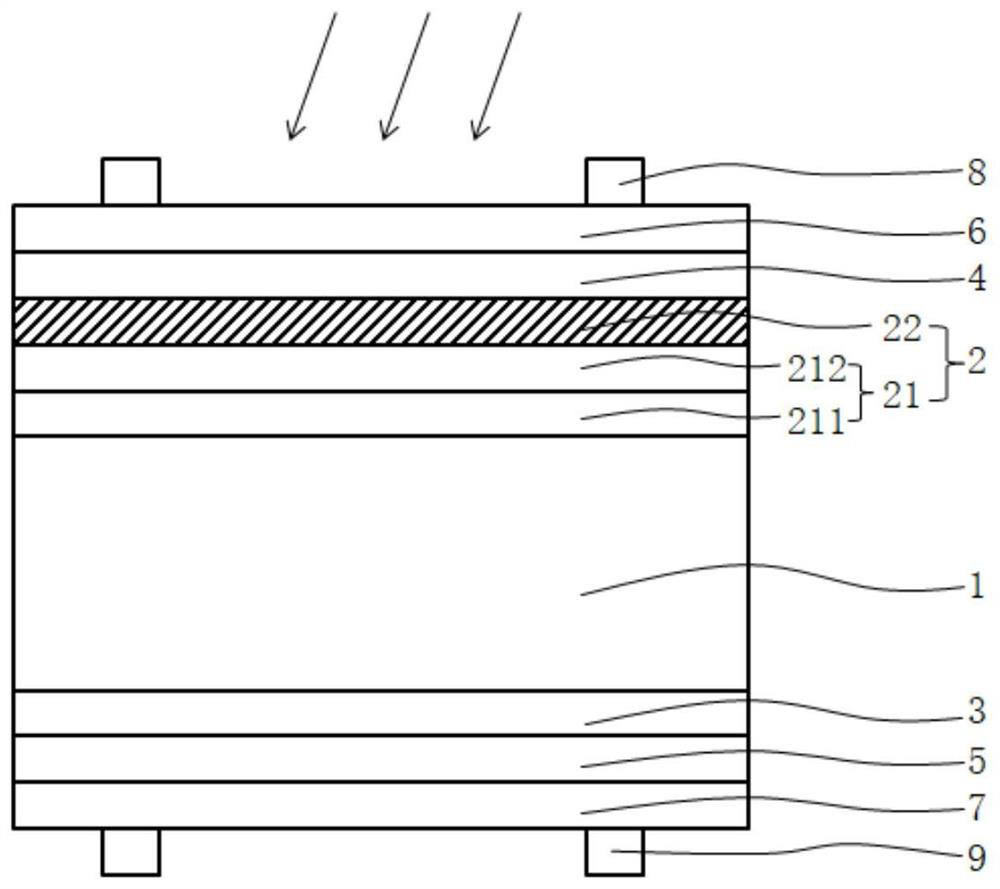

[0063] Please refer to figure 1 , figure 1 The middle arrow points to the irradiation direction of sunlight. In this embodiment, the intrinsic semiconductor composite layer 2 is only located on the front side of the semiconductor substrate layer 1 as an example for illustration.

[0064] In this case, preferably, the bandgap of the wide bandgap intrinsic layer 22 is 2.0eV˜9eV, for example, 2.0eV, 2.4eV, 2.8eV, 3.2eV and 9eV. Preferably, the ratio of the thickness of the wide bandgap intrinsic layer 22 to the thickness of the underlying intrinsic layer 21 is 1:1˜3:1, for example, 1:1, 2:1 or 3:1. Preferably, the thickness of the wide bandgap intrinsic layer 22 is 2nm-8nm, for example, 2nm, 5nm, 7nm or 8nm, and the thickness of the underlying intrinsic layer 21 is 1.3nm-3.3nm, for example, 1.3nm, 2nm , 3nm or 3.3nm.

[0065] The bottom intrinsic layer 21 includes: a first sub-bottom intrinsic layer 211; a second sub-bottom intrinsic layer 212 located on the surface of the fir...

Embodiment 2

[0084] Please refer to figure 2 In this embodiment, the intrinsic semiconductor compound layer 2 is only located on the back side of the semiconductor substrate layer 1 as an example for illustration.

[0085] For the intrinsic semiconductor composite layer 2 located on the back side of the semiconductor substrate layer 1, the valence band difference between the intrinsic semiconductor composite layer 2 and the semiconductor substrate layer 1 is 0.6eV to 7.9eV, for example 0.6 eV, 1.0eV, 2.1eV, or 7.9eV.

[0086] Doping oxygen atoms or carbon atoms in the wide bandgap intrinsic layer 22 can improve the valence band difference between the intrinsic semiconductor composite layer 2 on the back side of the semiconductor substrate layer 1 and the semiconductor substrate layer 1, and the high valence band difference is beneficial to The accumulation effect of the hole carriers in the photogenerated carriers is enhanced, so that the open circuit voltage of the heterojunction cell i...

Embodiment 3

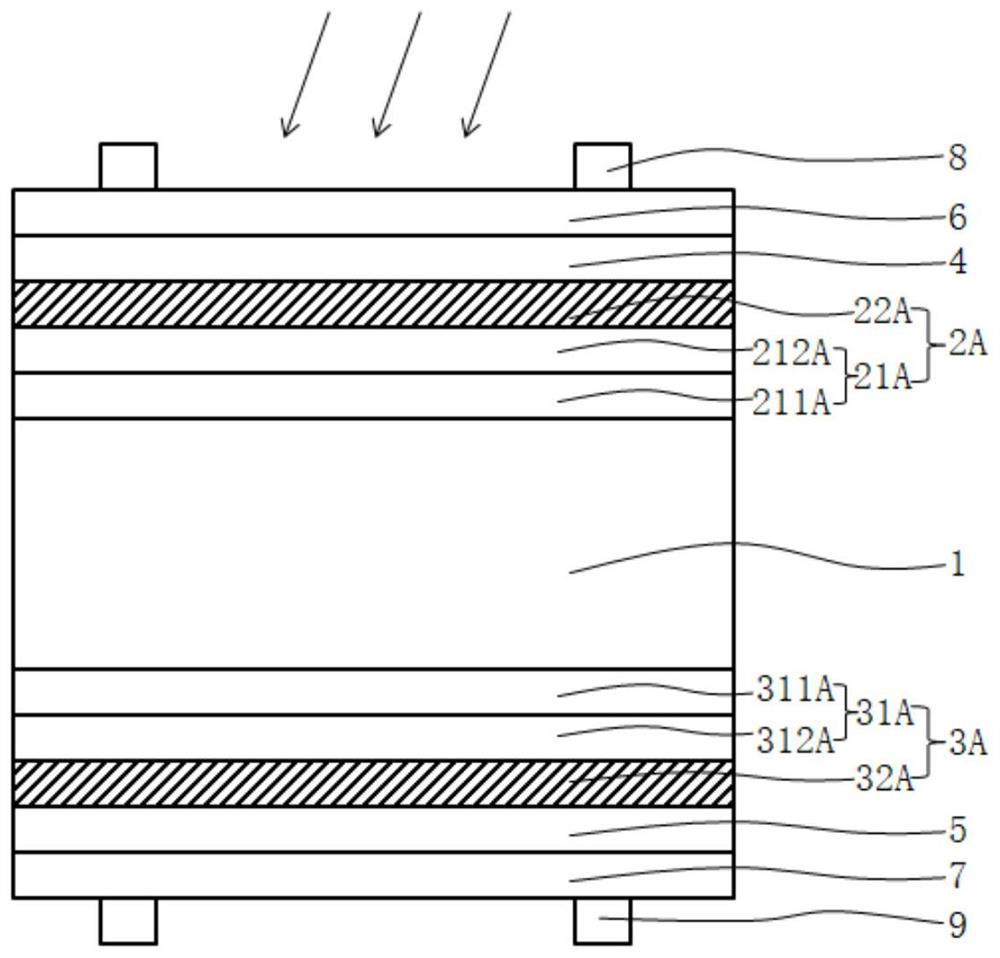

[0096] Please refer to image 3 In this embodiment, the intrinsic semiconductor composite layer is located on both sides of the semiconductor substrate layer 1, and the wide bandgap intrinsic layer is a single-layer structure (that is, N is equal to 1) as an example for illustration.

[0097] The intrinsic semiconductor composite layer includes a front intrinsic semiconductor composite layer 2A located on the front side of the semiconductor substrate layer 1 and a rear intrinsic semiconductor composite layer 3A located on the back side of the semiconductor substrate layer 1 .

[0098] The front intrinsic semiconductor composite layer 2A includes: the front bottom intrinsic layer 21A; the front wide bandgap intrinsic layer 22A located on the surface of the front bottom intrinsic layer 21A facing away from the semiconductor substrate layer 1, and the front wide bandgap intrinsic layer 22A. The bandgap of the intrinsic layer 22A is larger than the bandgap of the front bottom intr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com