Preparation process of silicon substrate on power insulator

A preparation process and insulator technology, which is applied in the field of integrated circuit material preparation, can solve the problem of difficulty in accurately controlling the thickness uniformity of the silicon layer of the top device, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The specific implementation of the method for preparing a silicon-on-insulator substrate provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

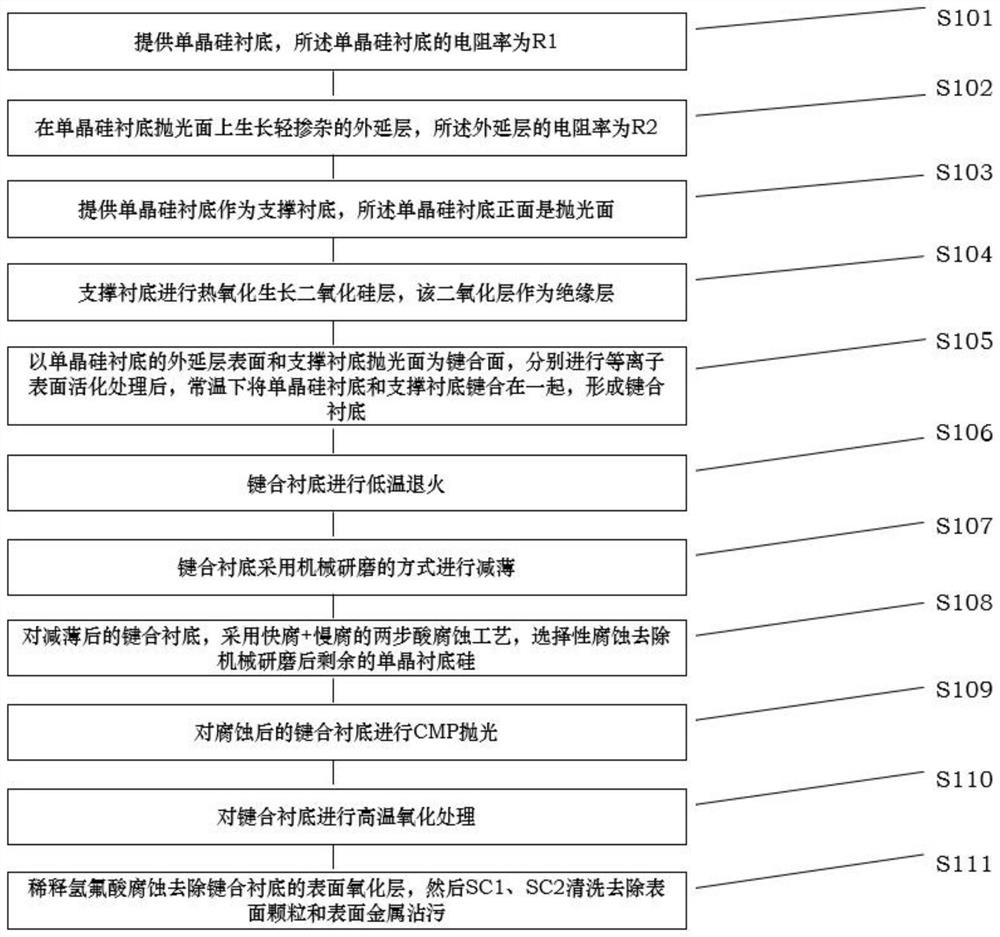

[0037] figure 1 Shown is the flow chart of the implementation steps of this specific embodiment, a preparation process of a silicon substrate on a power insulator, including the following steps:

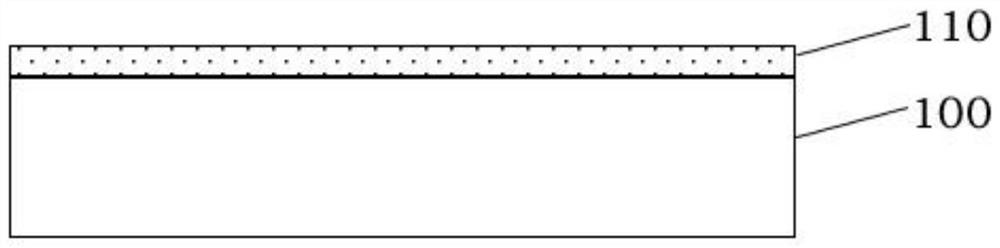

[0038] Step S101, providing a single crystal silicon substrate, the single crystal silicon substrate is a heavily doped substrate with a resistivity of R1;

[0039] Step S102, growing a lightly doped single crystal epitaxial silicon layer on the surface of the single crystal silicon substrate, the epitaxial silicon layer has the same doping type as the single crystal silicon substrate, and the resistivity of the epitaxial silicon layer is R2;

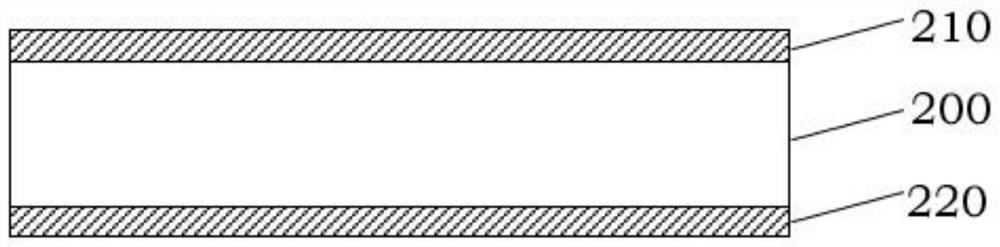

[0040] Step S103, providing a support substrate, the front surface of the support substrate is a polished surface;

[0041] Step S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com