Pressure sensor and preparation method thereof

A technology of pressure sensor and piezoresistor, which is applied in the field of sensors, can solve the problems of large vibration and shock load, poor linearity, poor plasticity and flexibility, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

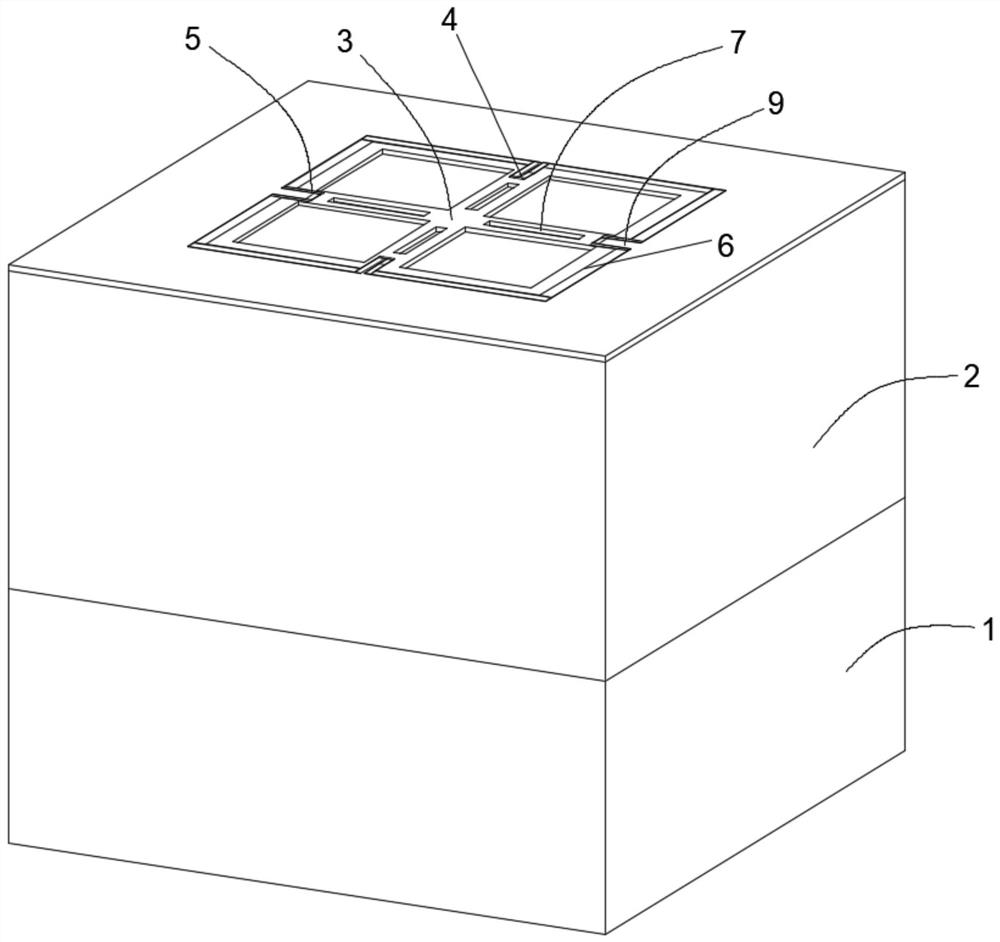

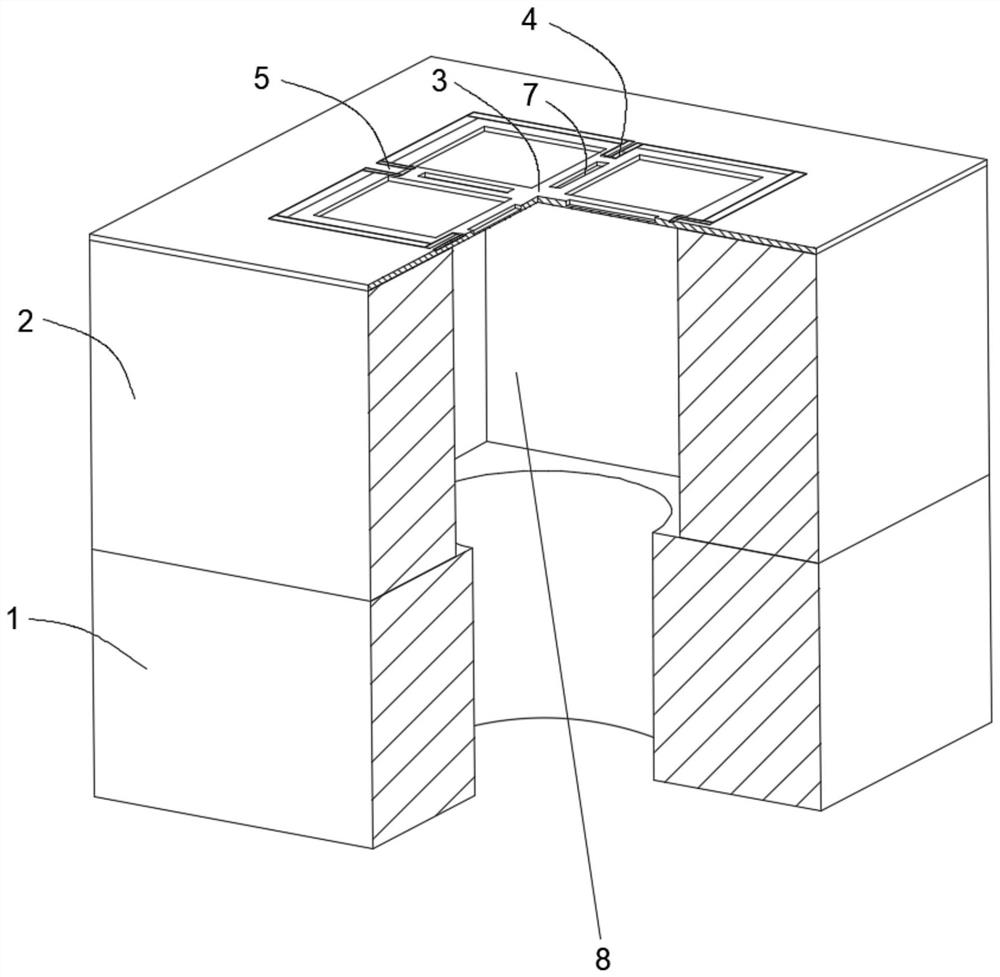

[0048] Such as figure 1 As shown, a pressure sensor, a MEMS piezoresistive pressure sensor designed and developed using MEMS technology, includes a glass base 1 and a silicon strain diaphragm 2 on the glass base 1, and the silicon strain diaphragm Sheet 2 is a silicon film with front beam film and back cavity structure formed by SOI wafer / silicon wafer through front etching and back cavity etching process;

[0049] Such as figure 1 or figure 2 As shown, one side of the glass base 1 is provided with a concave cavity, and the silicon strain diaphragm 2 includes an insulating dielectric layer on the front side and a silicon substrate covered by the insulating dielectric layer, wherein the silicon substrate is an N-type crystal plane SOI (Silicon-On-Insulator) silicon wafer or N-type silicon wafer, and the silicon strain diaphragm 2 and the glass base 1 with a concave cavity are anodically bonded, which can bond the non-bonding surface of the silicon wafer Thinning, because t...

Embodiment 2

[0059] This embodiment discloses a method for preparing a pressure sensor. Multiple groups of piezoresistors 4 are fabricated at the midpoint of the sideline of a square diaphragm made by a back cavity etching process, and the number of piezoresistors 4 in each group is arbitrary. In this embodiment, there are four pieces; the front surface of the silicon strain diaphragm 2 is shallowly etched with a cross-beam structure, and the piezoresistor 4 is located on the cross-beam structure and at the edge of the cross-beam structure, and the piezoresistor 4 is located in the stress concentration area . Specifically, the steps of the method include:

[0060] 1) Chip preparation, marking layer etching: For N-type crystal plane SOI (Silicon-On-Insulator) silicon wafer zero-layer alignment etching mark, thermal oxygen on the surface of the silicon wafer Silica, such as Figure 4A shown;

[0061] 2) Photolithographic varistor 4: photolithographic varistor 4 pattern in the SOI silico...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com