Cache data management method based on energy harvesting nonvolatile processor and medium

A non-volatile, caching data technology, applied to data error detection, electrical digital data processing, instruments, etc. in the direction of redundancy in computing, can solve the problem of increasing energy burden, backup redundancy recovery rollback operation, waste of energy And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

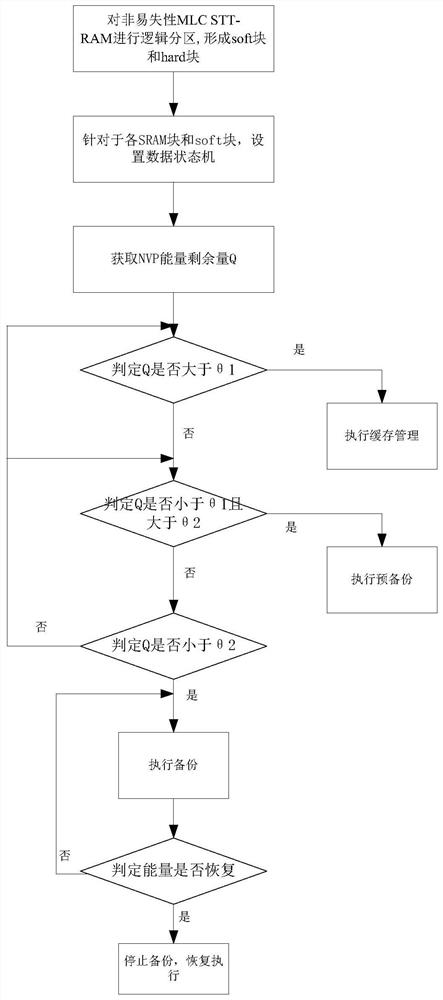

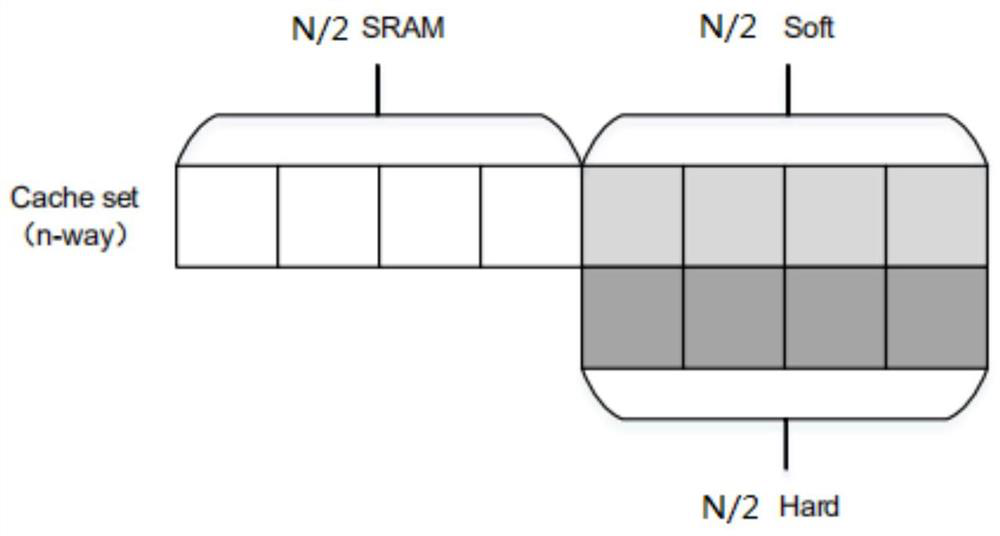

[0084] This embodiment discloses a cache data management method based on a non-volatile processor for energy harvesting, wherein the cache of the non-volatile processor is a hybrid cache based on a non-volatile memory, and the non-volatile processor includes Mixed cache (cache) and non-volatile main memory (main memory). In this architecture, the register file can be fully backed up by non-volatile flip-flop (NVFF) technology, and the hybrid cache consists of volatile memory (SRAM) and non-volatile memory (MLC STT-RAM). like figure 1 As shown in, the method of this embodiment includes the steps:

[0085] Step S1, logically partition the non-volatile memory MLC STT-RAM, and form soft blocks and hard blocks after logical partitioning.

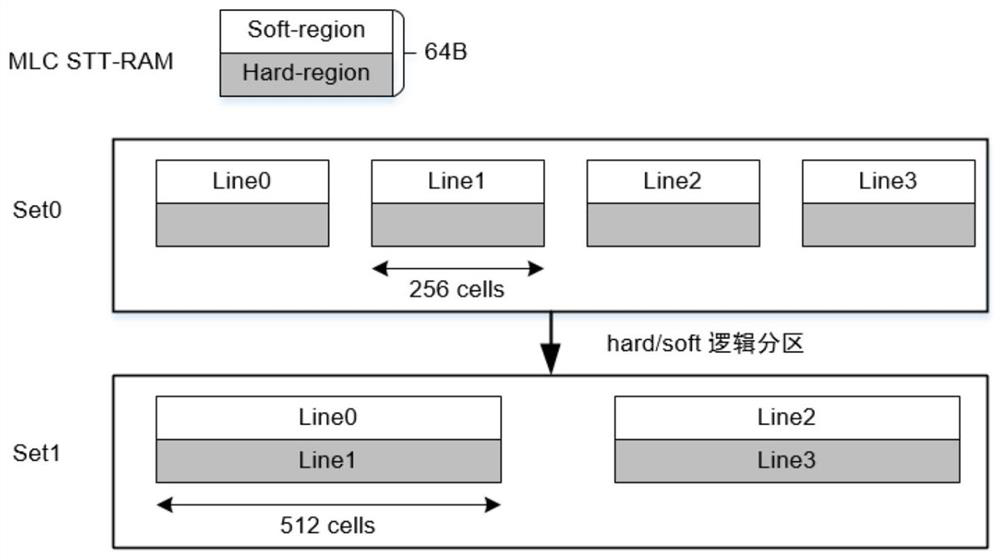

[0086] Each MLC STT-RAM block is 2 times the size of each SRAM block. Before the logical partition, in each MLC STT-RAM block, 1 / 2 are soft bits and 1 / 2 are hard bits. When logically partitioning the MLC STT-RAM, the adjacent physical blocks ...

Embodiment 2

[0135] This embodiment 1 discloses a cache data management device based on a non-volatile processor for energy harvesting. The cache of the non-volatile processor is a hybrid cache based on non-volatile memory, including volatile memory. SRAM and non-volatile memory MLC STT-RAM, the device includes:

[0136] Partitioning module: used to logically partition non-volatile MLC STT-RAM, and form soft blocks and hard blocks after logical partitioning;

[0137] The data state machine setting module is used to set n-bit registers for each volatile memory SRAM block and non-volatile soft block, and each cache block corresponds to 2 n state, when the cache block starts to enter the cache, the initial state is S 0 , after each transition time T, enter the next state, if a read or write access operation occurs, the state of the cache block is reset to the initial state S 0 , otherwise, if in (2 n -1) No access operation occurs on the cache block during ×T, then the cache block will rea...

Embodiment 3

[0148] This embodiment discloses a storage medium that stores a program. When the program is executed by a processor, the method for managing cache data based on an energy harvesting non-volatile processor described in Embodiment 1 is implemented, as follows:

[0149] The non-volatile memory MLC STT-RAM is logically partitioned, and soft blocks and hard blocks are formed after logical partitioning;

[0150] For each volatile memory SRAM block and non-volatile soft block, an n-bit register is set respectively, and each cache block corresponds to 2 n state, when the cache block starts to enter the cache, the initial state is S 0 , after each transition time T, enter the next state, if a read or write access operation occurs, the state of the cache block is reset to the initial state S 0 , otherwise, if in (2 n -1) No access operation occurs on the cache block during ×T, then the cache block will reach state and remain in this state until the cache block is accessed or replac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com