On-chip CMOS power amplifier with temperature compensation function

A power amplifier and temperature compensation technology, which is applied in the direction of power amplifiers, etc., can solve the problems of circuit output power gain reduction and temperature influence, and achieve precise changes in gain and output power, reduce chip area, and simplify matching circuit structure. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

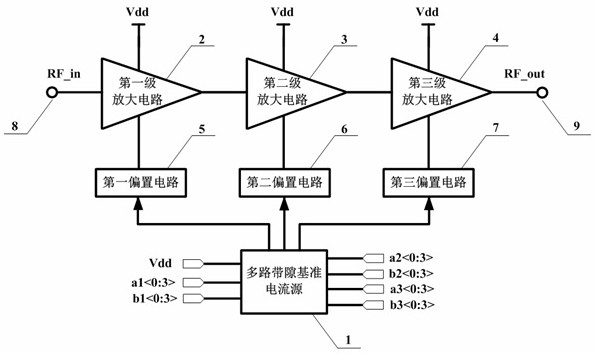

[0034] This embodiment discloses a CMOS power amplifier with temperature compensation function on chip. figure 1As shown, the power amplifier includes a multi-channel bandgap reference current source 1, a first-stage amplifying circuit 2, a second-stage amplifying circuit 3, a third-stage amplifying circuit 4, a first bias circuit 5, and a second bias circuit 6 and the third bias circuit 7, the three amplifying circuits are connected in turn, wherein the radio frequency signal input port 8 is connected to the input end of the first stage amplifying circuit 2, and the output end of the first stage amplifying circuit 2 is connected to the second stage amplifying circuit The input end of 3 is connected, the output end of the second-stage amplifying circuit 3 is connected with the input end of the third-stage amplifying circuit 4, and the output end of the third-stage amplifying circuit 4 is connected with the radio frequency signal output total port 9;

[0035] The current input...

Embodiment 2

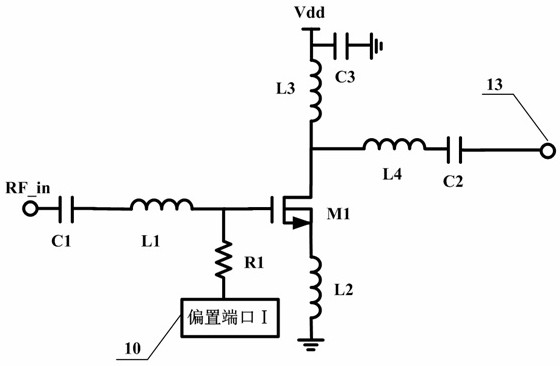

[0040] This embodiment discloses a CMOS power amplifier with on-chip temperature compensation function. On the basis of Embodiment 1, this embodiment makes further limitations on three bias circuits and three-stage amplifying circuits.

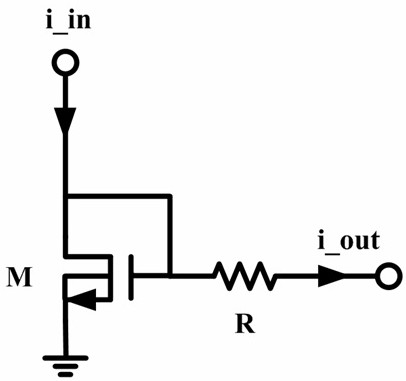

[0041] The first bias circuit 5, the second bias circuit 6 and the third bias circuit 7 have internal circuit structures such as figure 2 As shown, the circuit structures of the three are the same, including an NMOS transistor M and a resistor R, wherein the source of the NMOS transistor M is grounded, the gate and the drain are short-circuited, and the drain of the NMOS transistor M is connected to the current input terminal connected to i_in, the gate of the NMOS transistor M is connected to one end of the resistor R, and the other end of the resistor R is connected to the current output terminal i_out. The bias circuit and the NMOS tube in the amplifier form a mirror current, and the current input at the i_in terminal is mirrored to the NM...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com