Method for forming semiconductor structure and semiconductor structure

A semiconductor and patterning technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problem of increasing the aspect ratio of dielectric layers and capacitor contact holes, increasing the size of trenches, and affecting the size of capacitor contact holes, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

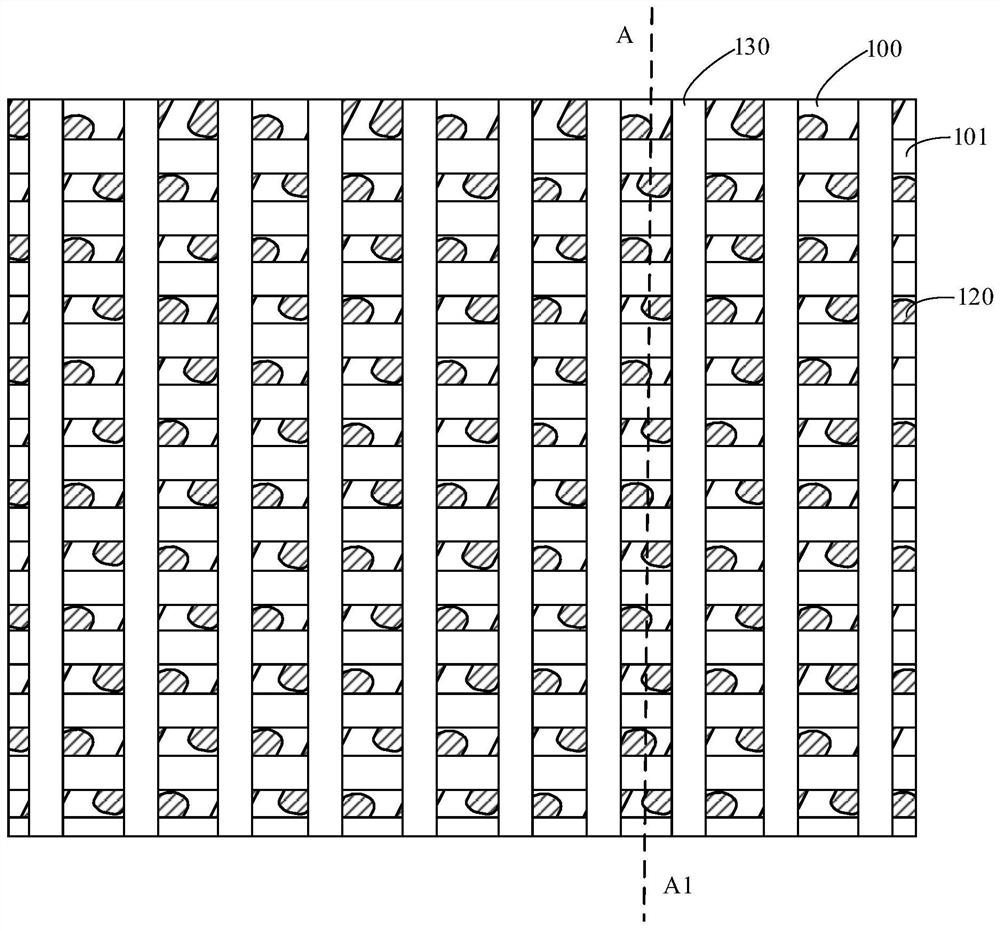

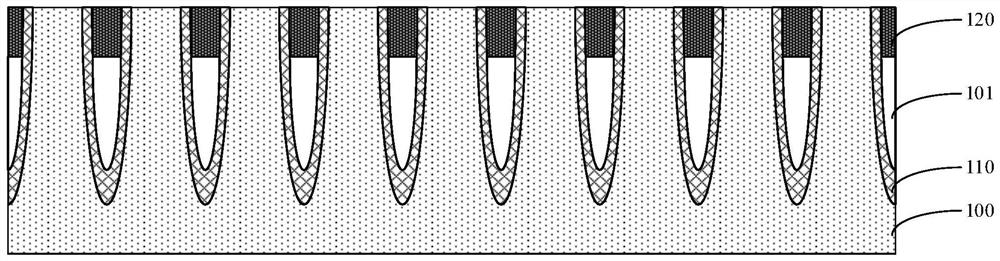

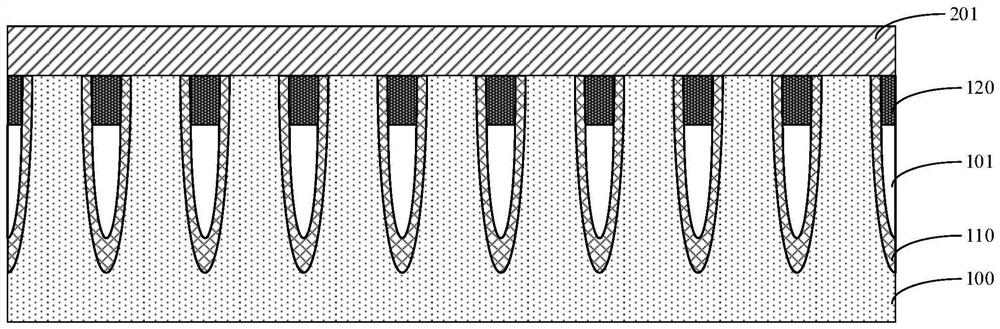

[0031] At present, the distance between adjacent bit line structures is also gradually reduced, which will lead to the increase of the aspect ratio of the dielectric layer and the capacitor contact hole formed between adjacent bit line structures; in the patterned sacrificial layer, the phase In the process of trenches required for the dielectric layer between adjacent bit line structures, due to the large aspect ratio of the dielectric layer, the trenches formed by patterning also have a large aspect ratio, which may cause etching of the bottom sacrificial layer Residue, the etching residue will cause the adjacent capacitor contact holes to be connected in the subsequent process of forming the capacitor contact hole, thus affecting the yield of the semiconductor structure; if the etching residue is etched twice, the size of the trench will be reduced becomes larger, thereby affecting the size of the capacitor contact hole formed later.

[0032] In order to solve the above pro...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com