A crc16-based single-bit error correction fpga implementation method

A technology of CRC16 and an implementation method, applied in the computer field, can solve the problems of large resource consumption, waste of resources, low efficiency, etc., and achieve the effects of high data processing efficiency, reducing data bit width, and reducing address space.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

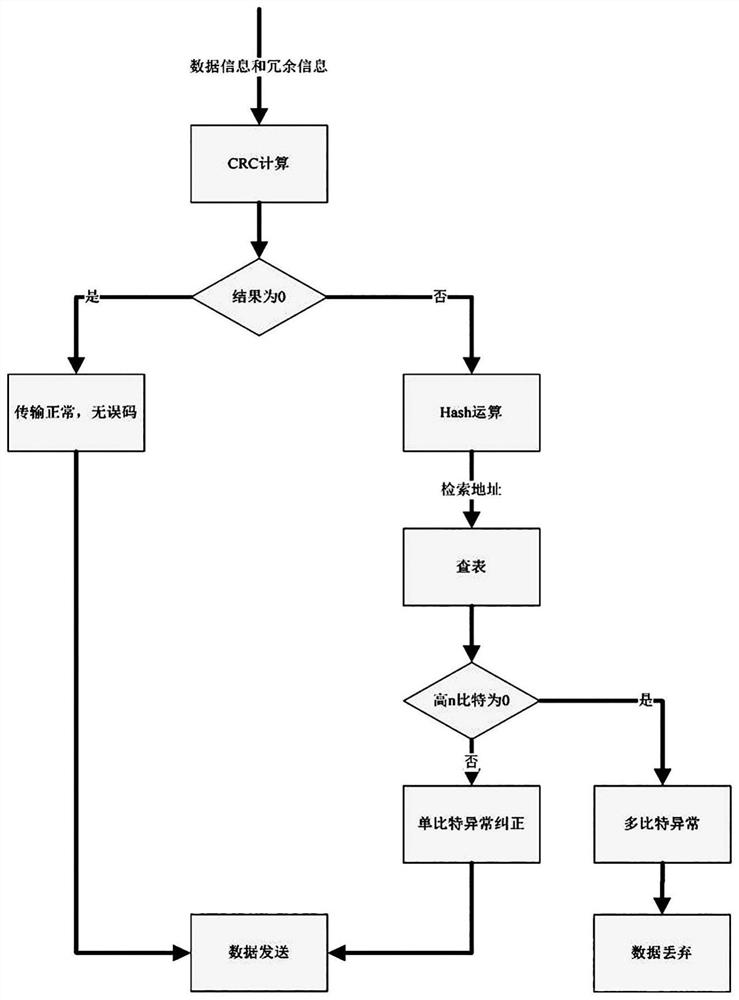

[0031] In order to clearly illustrate the technical features of the solution of the present invention, the solution will be further elaborated below in conjunction with the accompanying drawings and through specific implementation methods.

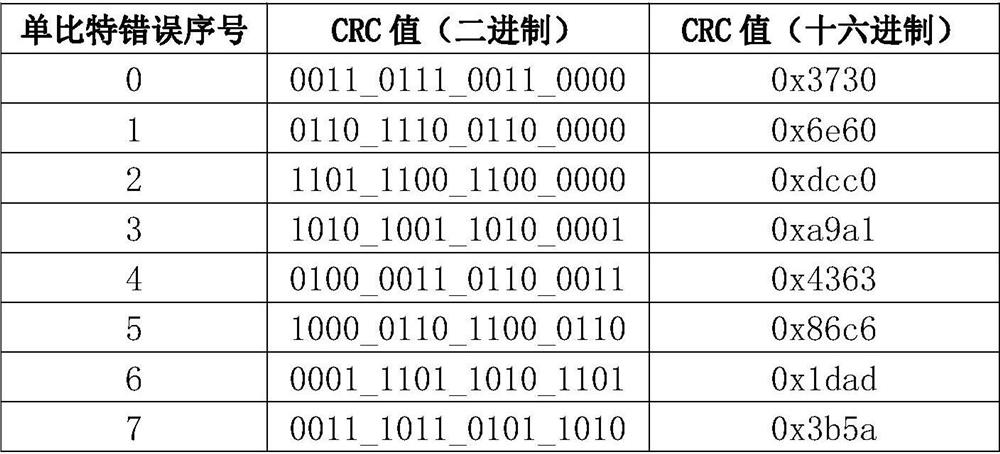

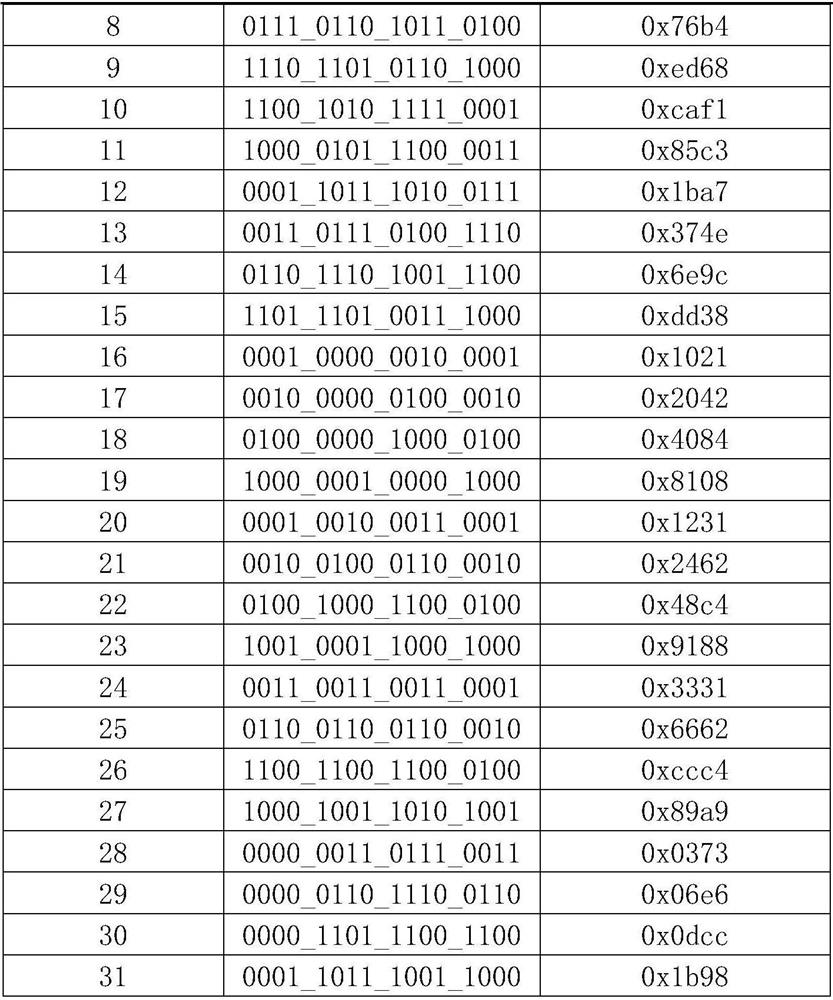

[0032] The calculation value of the check code at the receiving end is only related to the transmission error and the generator polynomial, and has nothing to do with the transmitted information data. Regarding the above conclusions, a brief explanation is given by taking the production polynomial of CRC-16 as x16+x12+x5+1, as shown in Table 1.

[0033] Table 1 CRC value corresponding to a single bit error

[0034]

[0035]

[0036] In this example, if figure 2 and image 3 As shown in , it is a single-bit error correction FPGA implementation method based on CRC16, including a data cache module, a read cache control module, an error judgment arbitration module and a transmission control module, wherein the error judgment arbitrati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com