Multi-core tensor processor of neural network

A neural network and processor technology, applied in the field of artificial intelligence chips, can solve the problems of unfavorable computing efficiency, not widely used, redundant instructions, etc., to achieve the effect of improving computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

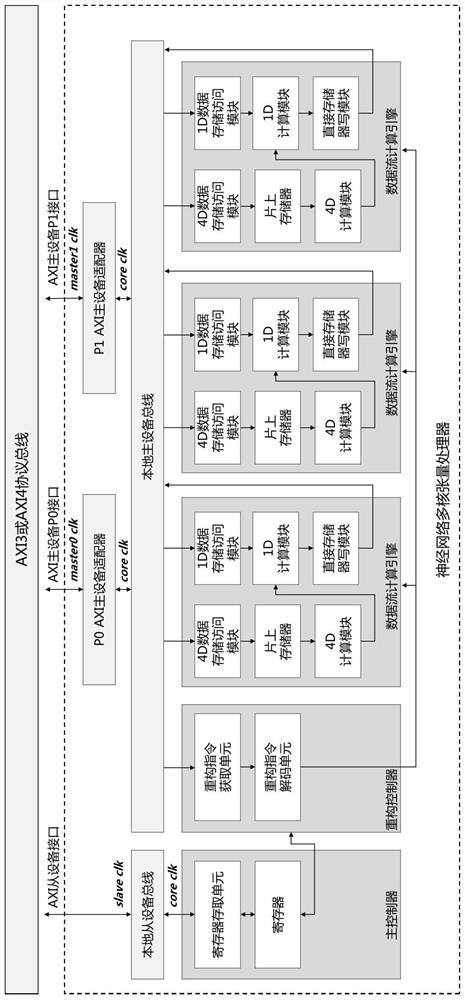

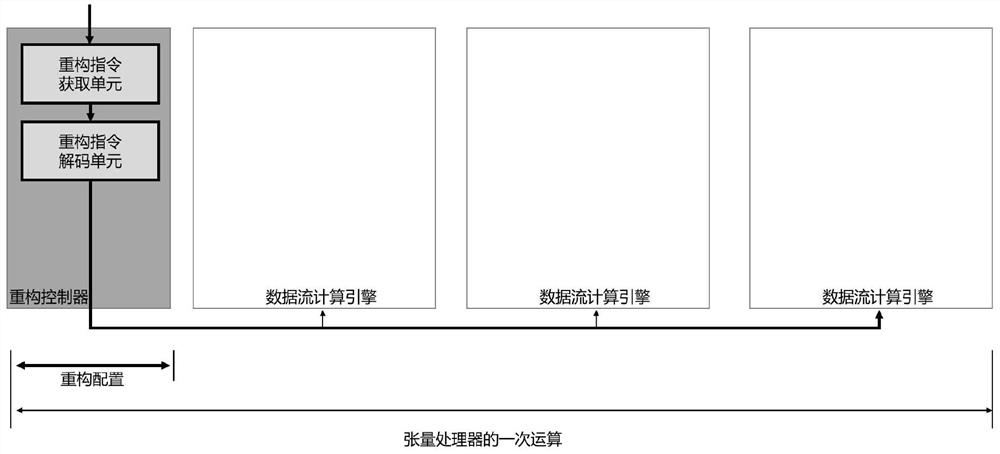

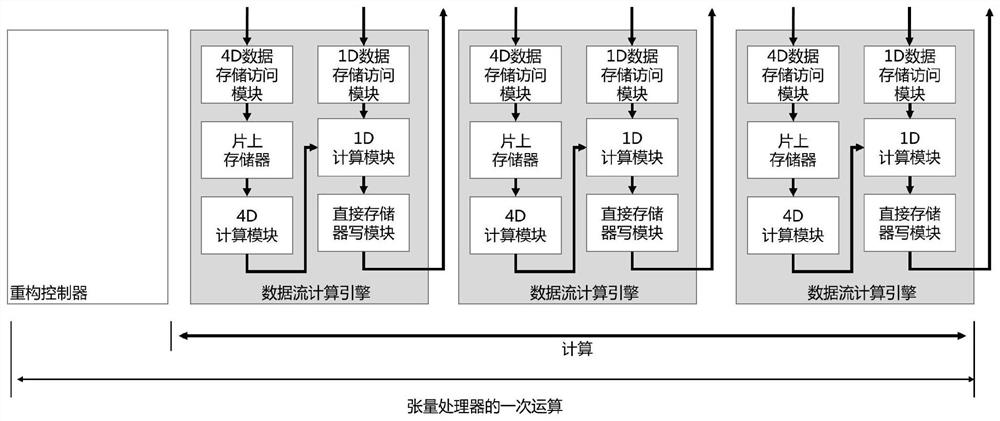

[0048] Such as figure 1 As shown, the technical solution of this embodiment is to provide a hardware architecture of a neural network multi-core tensor processor, figure 1 shown. It is mainly composed of three parts: Host Controller, Reconfiguration Controller and multiple Data-flow Computing Engines.

[0049] In order to improve the flexibility of system integration, the tensor processor adopts the asynchronous clock scheme between the system core and the AXI bus interface. The system uses four completely independent asynchronous clocks to realize the isolation between the tensor processor core and the external system. Among them, the AXI slave device interface uses one AXI slave device bus clock (slave clk), the AXI master device interface uses two AXI master device bus clocks (master0 clk and master1 clk), and the tensor processor core uses the core clock (coreclk).

[0050] The role of the main controller is to provide external control and status interfaces, so that ext...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com