Foreground time error correction circuit of multi-channel time domain interleaved data converter

A technology for interleaving data and correcting circuits, applied in analog/digital conversion calibration/testing, analog/digital conversion, code conversion, etc. performance degradation and other issues, to achieve the effect of reducing stability requirements, reducing output data rate, and reducing the probability of enabling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0090] The present invention aims at the difficulty of correcting the channel time error of the ultra-high-speed time-domain interleaving data converter with more than 10 channels, and provides a front-end error automatic correction circuit to compensate the channel time error generated by the converter during the process of tape-out and actual use. Matching, reducing error and spurious signal components, improving parameters such as spurious-free dynamic range and signal-to-noise ratio, and improving the overall performance of the data converter.

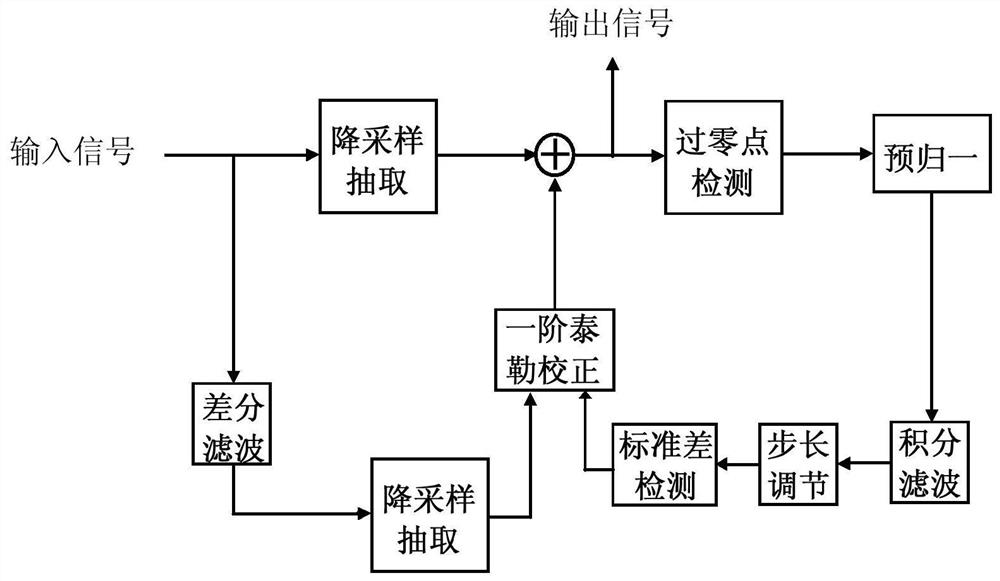

[0091] The overall block diagram of the circuit of the present invention is as figure 1 shown. The circuit includes a down-sampling channel data extraction circuit, a zero-crossing detection circuit, a pre-normalization circuit, a negative feedback integration circuit, a convergence detection circuit, and a first-order Taylor expansion correction circuit. Because the clock distribution in the ultra-high-speed multi-channel time-do...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com