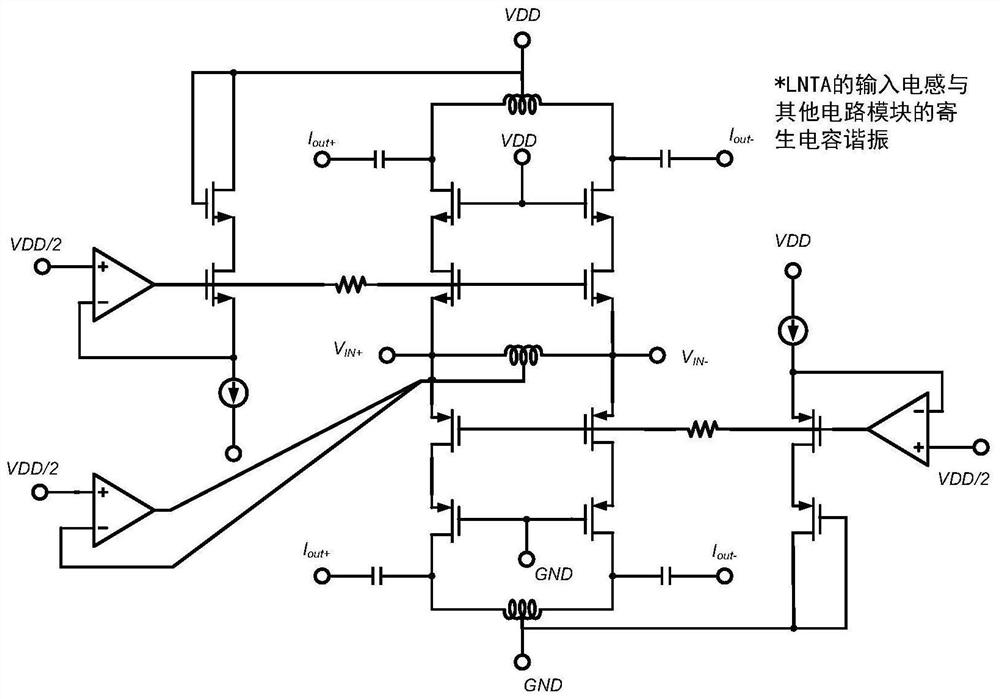

CMOS low-distortion low-noise amplifier circuit

A low-noise amplifier and low-distortion technology, applied in the direction of amplifiers, differential amplifiers, DC-coupled DC amplifiers, etc., can solve problems such as low power consumption and noise, and difficult large-signal interference environments

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0047] The low noise amplifier circuit provided in this embodiment is realized by 180nm radio frequency CMOS technology, powered by 1.8V voltage, and the power consumption of the circuit is 18mW. Figure 6 The S11 simulation result diagram of the LNA is given, indicating that when S11 Figure 7 The noise figure result is given, and its minimum noise figure NF is about 2.84dB; Figure 8 The IIP3 simulation results in its band are given: the maximum value is 22.5dBm, and a two-tone test frequency interval of 10MHz is used here. It can also be seen that its power compression point P1dB>2.5dB; Figure 9 It is the simulation result graph of Blocker NF in the case of blocking interference, in P blocker =0dBm and 100MHZ frequency offset condition, the noise performance at 1GHz point frequency is NF=3.3dB; Figure 10 The gain curve of the low-noise amplifier is given, and it is noted that its voltage gain is 4dB, and the peak value of the transconductance gain reaches 100mS within th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com