Transistor tube base and transistor airtight packaging structure

A technology of transistors and tube bases, which is applied in the field of transistor bases and transistor hermetic packaging structures, and can solve problems such as low cost, high speed of TO tube bases, and high heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

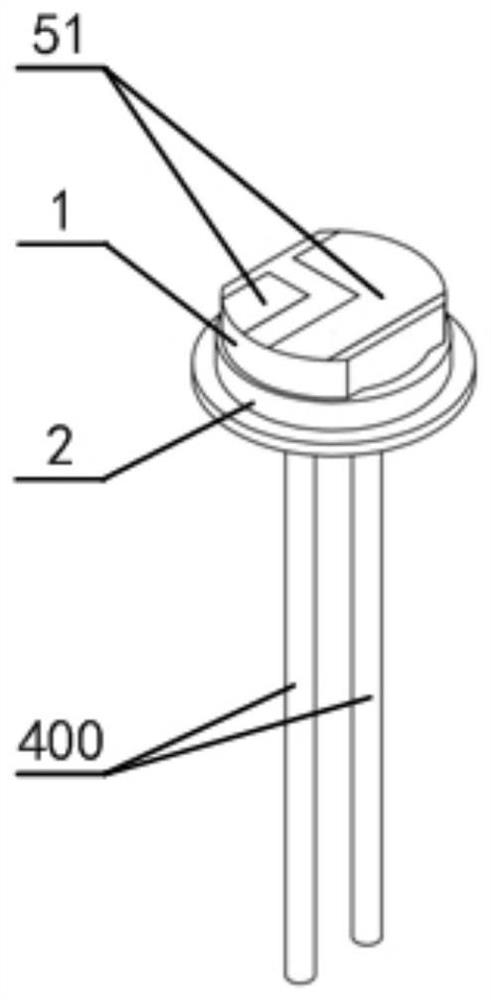

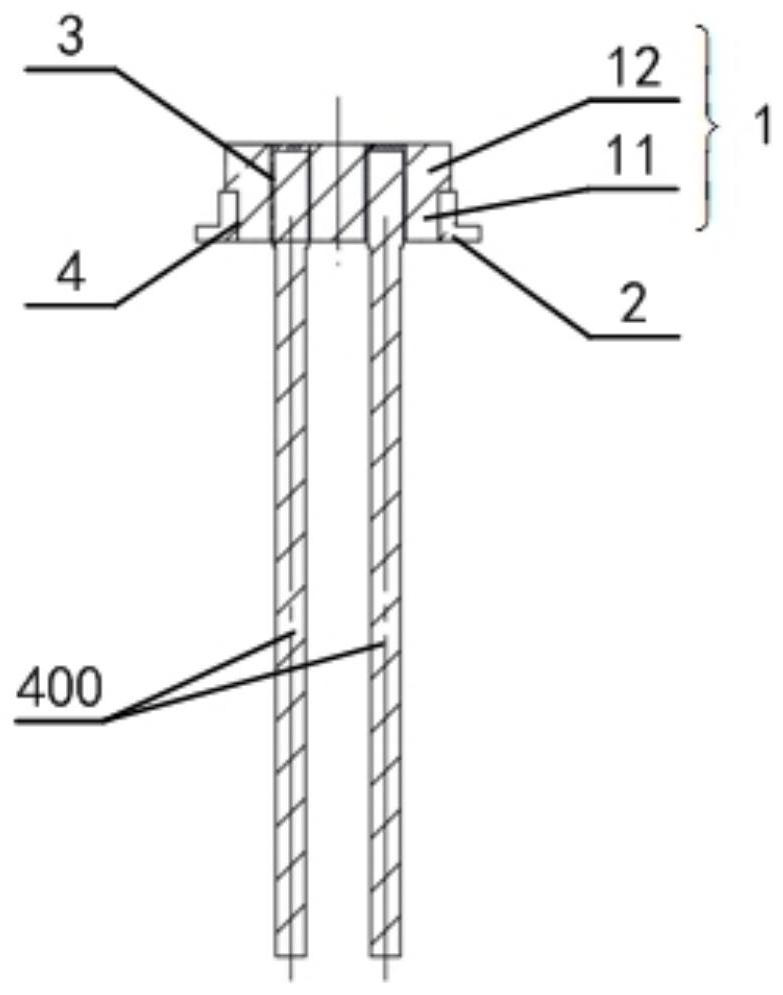

[0052] Such as Figure 1~3 As shown, the first transistor base provided in this embodiment includes an insulating base 1 and a circumferentially closed metal base 2, wherein the top surface of the insulating base 1 is used to place a transistor chip 300; the insulating base 1 is provided with at least one conductive channel 3, and the outer peripheral surface of the insulating base 1 is sealed and connected to the inner ring surface of the circumferentially closed metal base 2 through a filler 4, wherein the top end of the conductive channel 3 is used for a The chip pins of the transistor chip 300 are electrically connected one by one, and the bottom end of the conductive channel 3 is used for electrically connecting the external wiring parts of the transistor one by one.

[0053] Such as Figure 1~3 As shown, in the specific structure of the transistor base, the insulating base 1 is used to realize the circumferential sealing between the metal base 2 and the conductive chann...

Embodiment 2

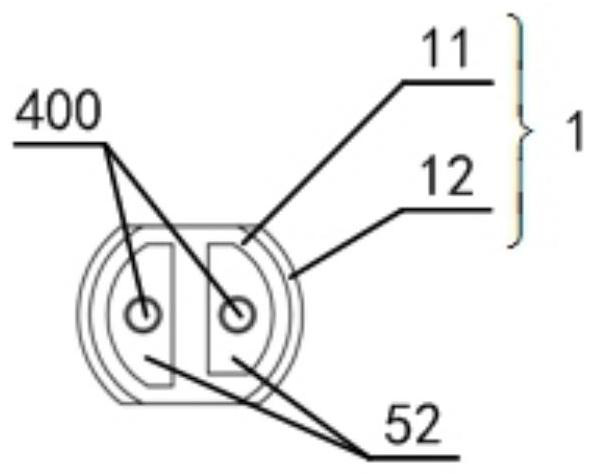

[0062] Such as Figure 4~6 As shown, on the basis of the technical solution of the first embodiment, this embodiment provides the second transistor base, which differs from the first transistor base described in the first embodiment in that there is no transistor pin 400 It is designed that the second conductive pad 52 is directly used as the external connection member of the transistor corresponding to the conductive channel 3 . For example, when a conventional diode chip is packaged in the tube, one of the second conductive pads 52 can be used as an anode pad, and the other second conductive pad 52 can be used as a cathode pad, which can also be conveniently used in actual circuit boards.

[0063] The technical effect of this embodiment can be directly derived by referring to the technical effect of the first embodiment, and will not be repeated here.

Embodiment 3

[0065] Such as Figure 7 As shown, this embodiment provides a third type of transistor base on the basis of the technical solution of Embodiment 1, which is different from the first type of transistor base in Embodiment 1 in that: the conductive channel 3 The top surface protrudes from the top surface of the insulating base 1, the first conductive pad 51 is arranged on the top surface of the conductive channel 3; the transistor chip 300 is arranged on the top surface of the insulating base 1 , and connect the chip pins on the transistor chip 300 and the first conductive pad 51 through gold wires; the insulating base 1 and the filler 4 are sealed with the ring-to-enclosed metal base 2 using the same material .

[0066] Optimally, the transistor chip 300 is disposed on the first conductive pad 51 located on the top surface of the conductive channel 3 .

[0067] The technical effect of this embodiment can be directly derived by referring to the technical effect of the first emb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com