Failure analysis sample preparation method and failure analysis sample

A failure analysis sample and technology to be analyzed, which is applied in the direction of electronic circuit testing, measuring devices, instruments, etc., and can solve problems such as difficult processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

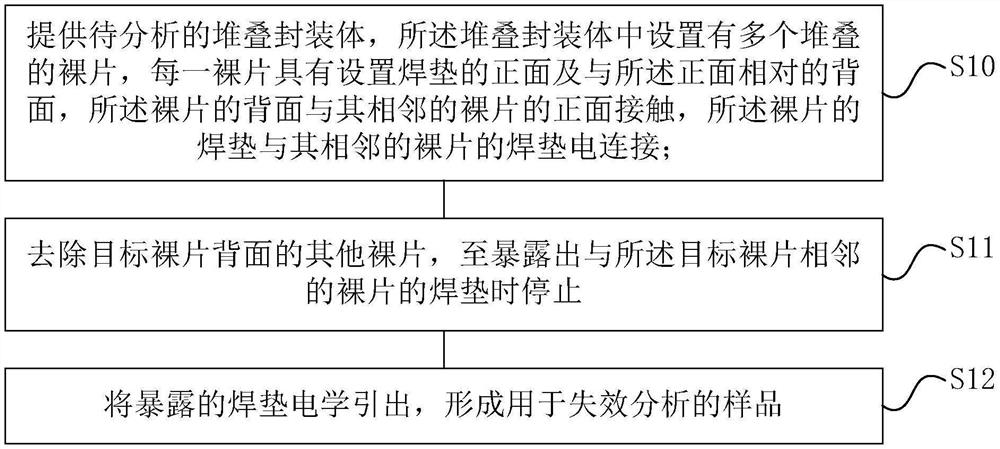

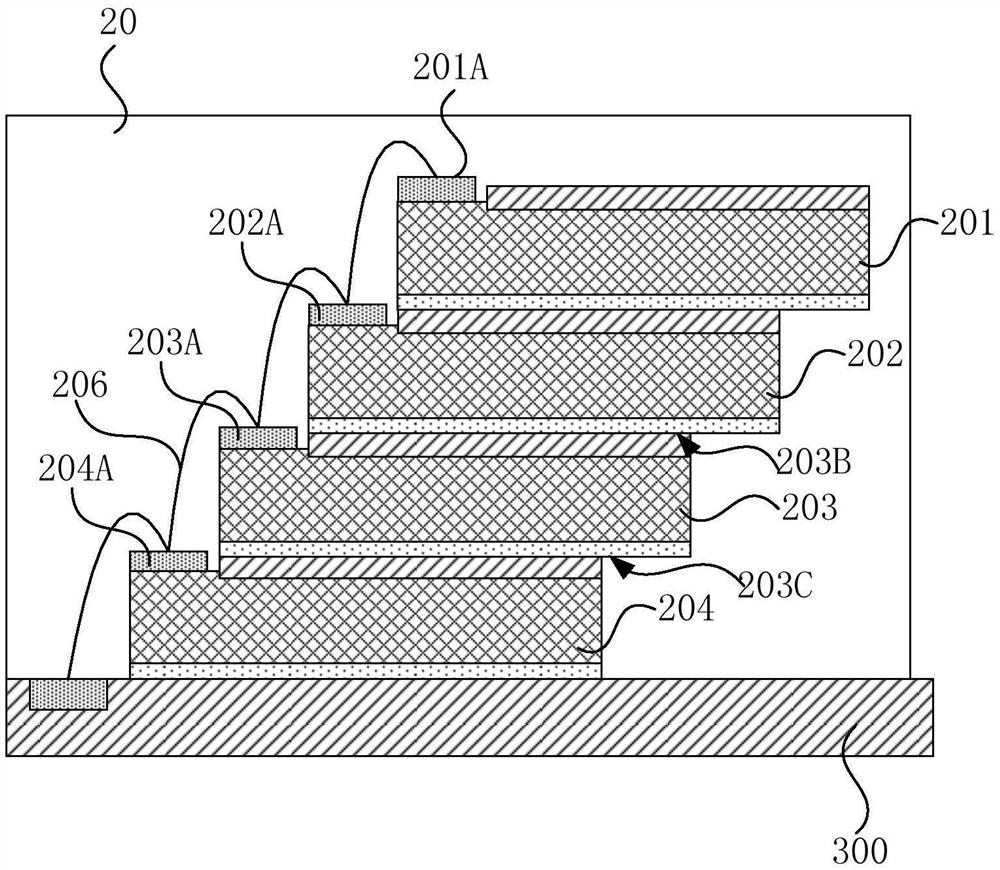

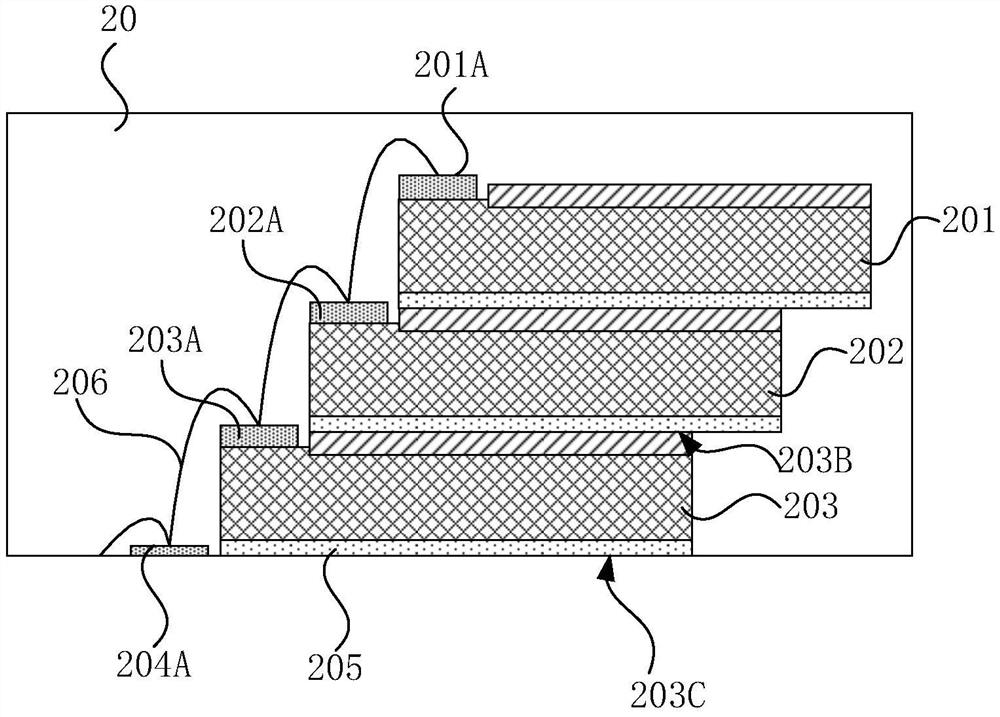

[0024] The method for preparing the failure analysis sample provided by the present invention and the specific implementation of the failure analysis sample will be described in detail below in conjunction with the accompanying drawings.

[0025] At present, the conventional failure analysis sample preparation method is to use the method of front and back grinding (polish) to grind from the front of the die to the bonding pad of the target die, and to grind from the back of the die to the crystal back of the target die, so as to obtain a single target die, and then stick the test probe card (prober card) on the solder pad, then dynamic hot spot (dynamic hotspot) analysis can be performed.

[0026] However, this preparation method has the disadvantage of high sample preparation failure rate, and when the probe card is used to test the failure analysis sample, the probe card will be damaged, resulting in an increase in the analysis cost.

[0027] The inventors have found through...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com