Clock data recovery method and circuit

A clock data recovery and circuit technology, applied in the field of network communication, can solve problems such as phase jitter amplification, achieve the effect of reducing spurs, wide frequency coverage, and realizing fractional frequency division

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

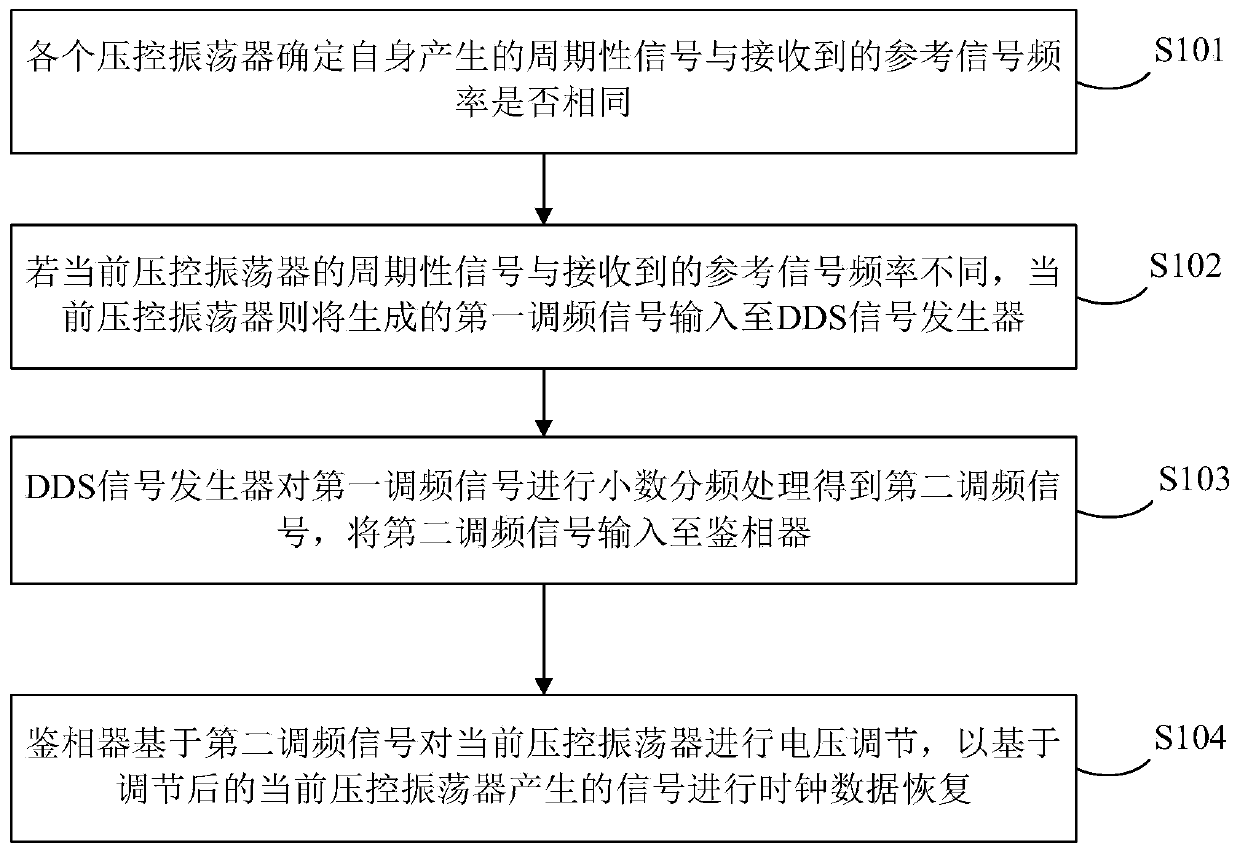

[0037] figure 1 It shows a schematic flowchart of a clock data recovery method provided in this embodiment, including:

[0038] S101. Each voltage-controlled oscillator determines whether the frequency of the periodic signal generated by itself is the same as that of the received reference signal.

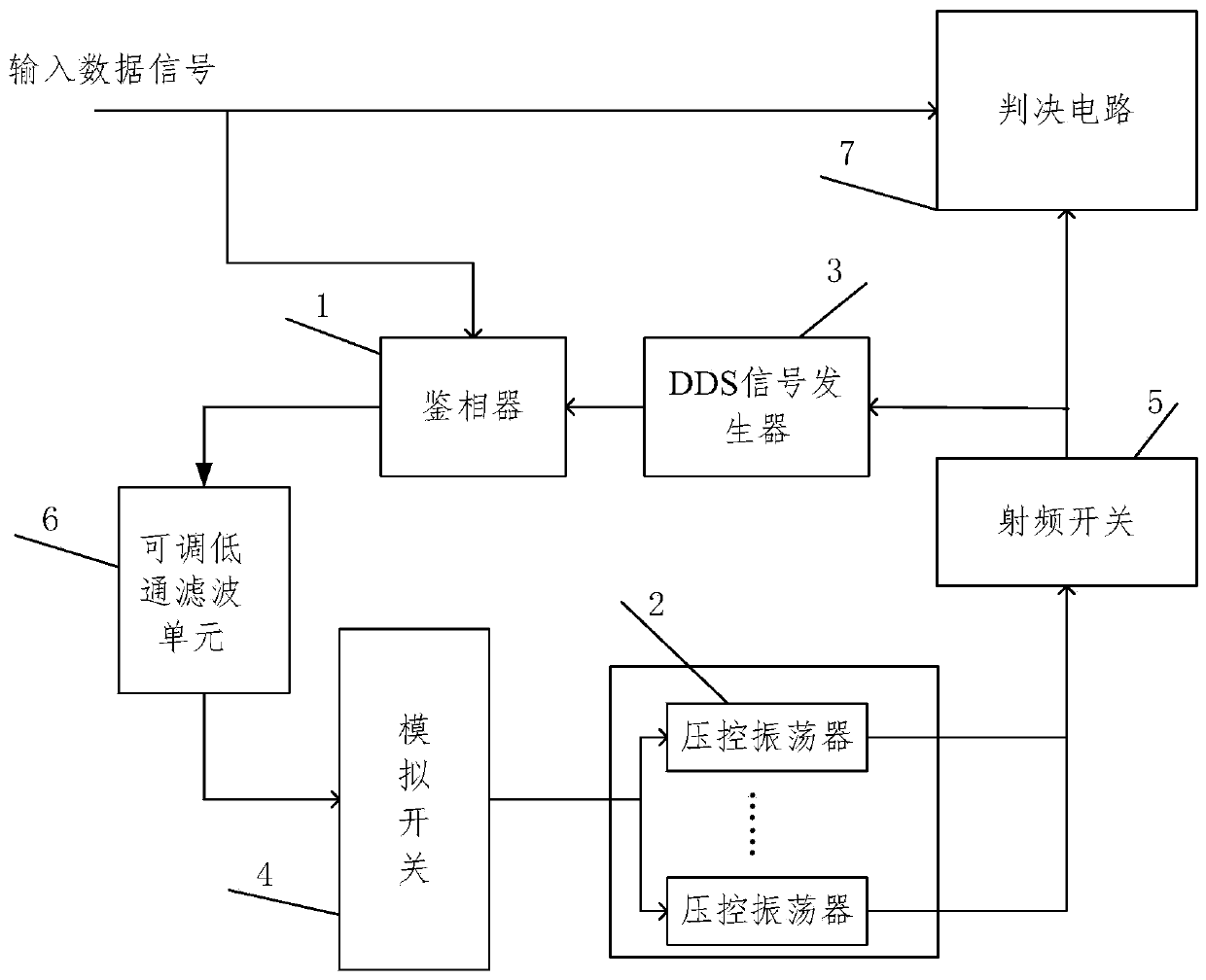

[0039] In implementation, the phase detector can adjust the voltage of the voltage-controlled oscillator according to the frequency modulation signal generated by each voltage-controlled oscillator (at least two) based on the periodic signal generated by itself and the received reference signal, so as to be based on the The signal generated by the regulated voltage-contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com