Three-dimensional NAND memory device structure and preparation method thereof

A storage device, three-dimensional technology, applied in the field of memory, can solve problems such as damage to the top layer structure, lower structural yield of three-dimensional NAND storage devices, reliability failure, etc., and achieve the effect of low process complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

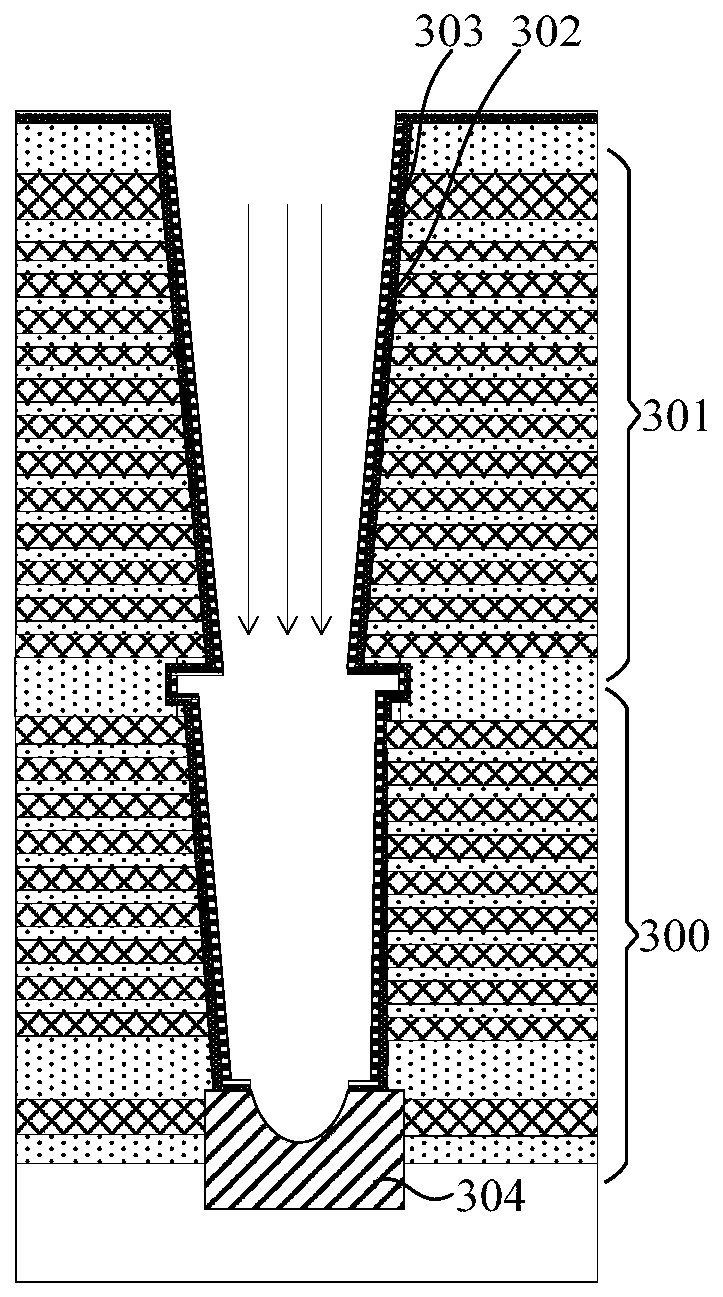

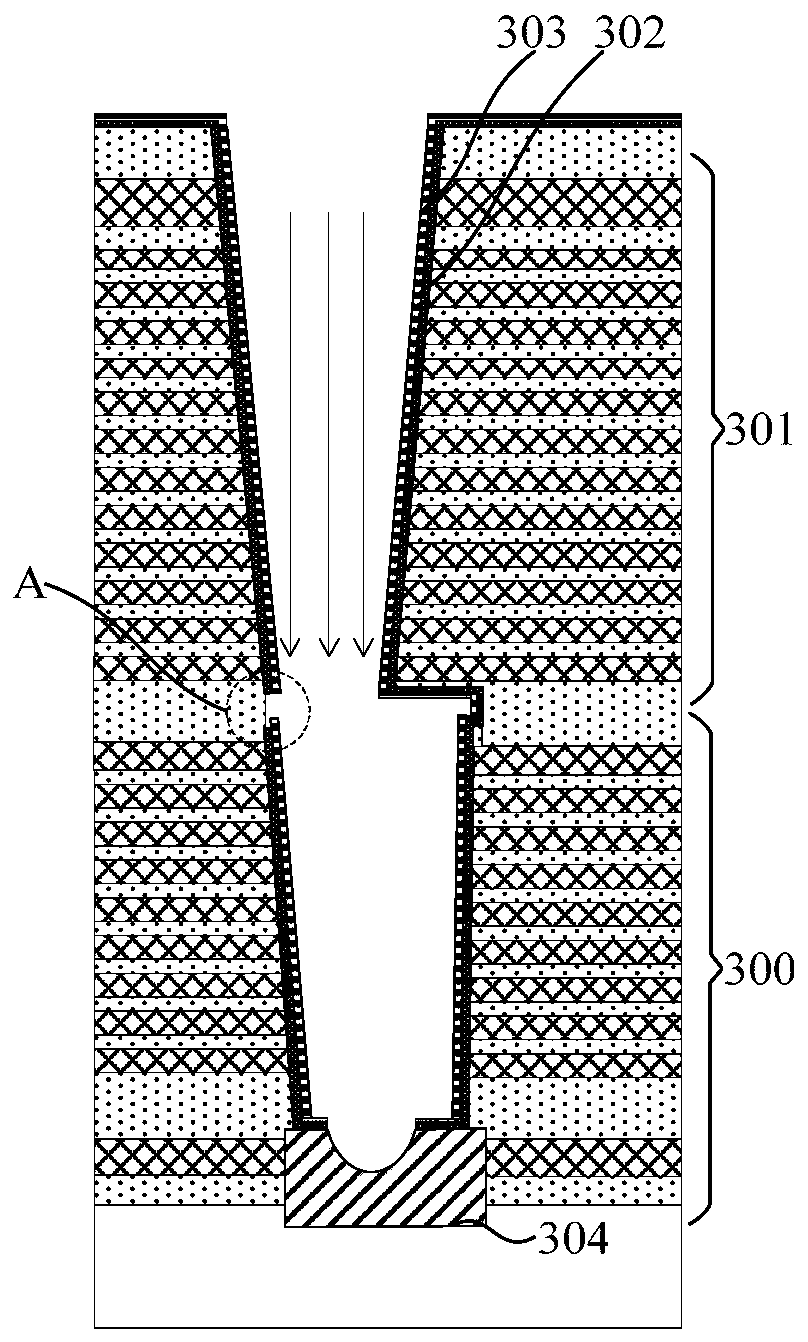

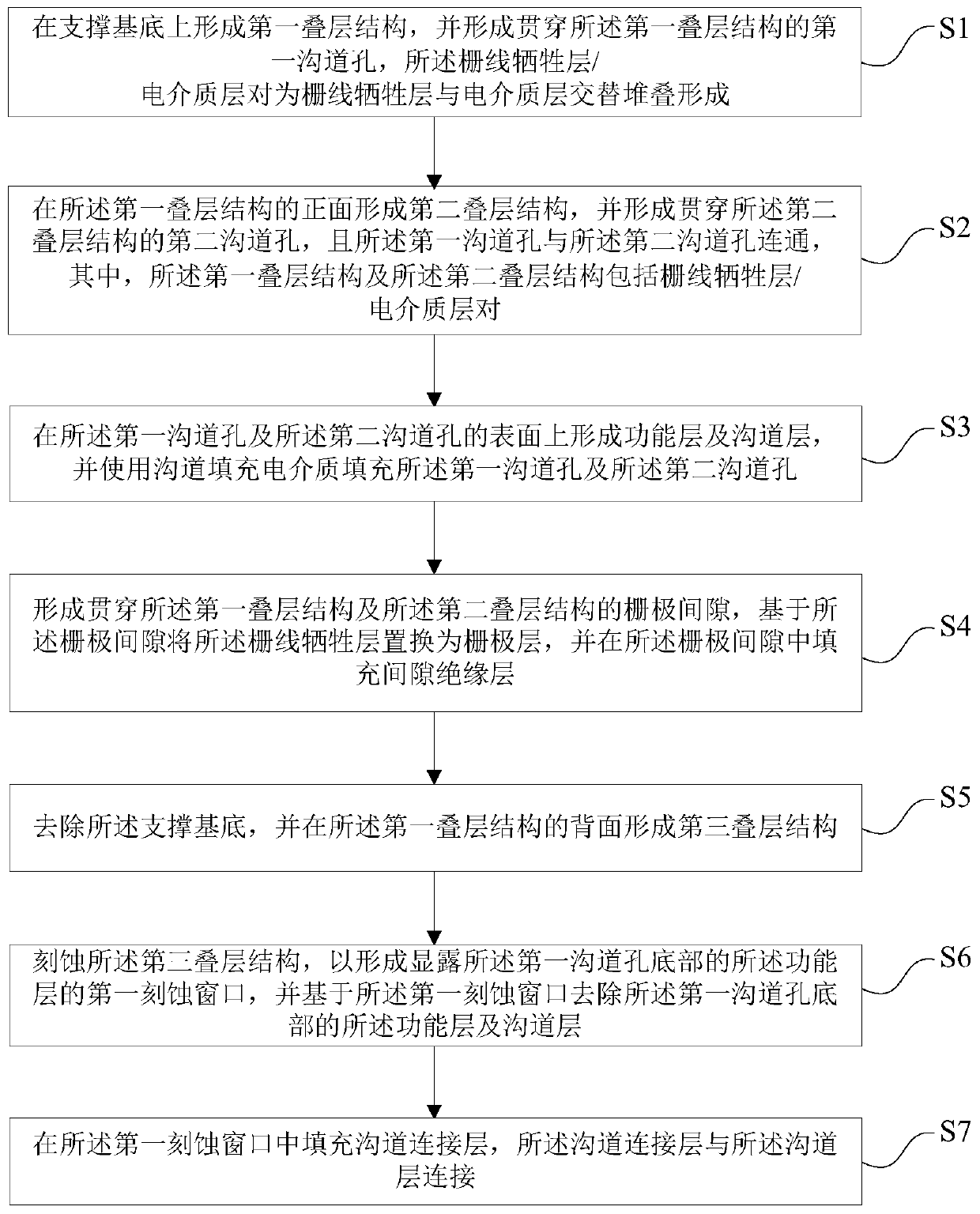

[0126] like image 3 As shown, in order to solve the above problems, this embodiment provides a method for preparing a three-dimensional NAND memory device structure, including the following steps:

[0127] like image 3 , Figure 4 to Figure 6As shown, step S1 is firstly performed to form a first laminated structure 101 of a grid line sacrificial layer 105 / dielectric layer 106 pair on a support substrate 100 (such as Figure 4 ), and form a first channel hole 102 penetrating through the first stacked structure 101 (as shown in Figure 5 shown).

[0128] As an example, the gate line sacrificial layer 105 may be a nitride layer, such as silicon nitride; the dielectric layer 106 may be an oxide layer, such as silicon oxide.

[0129] The first stacked structure 101 may include any suitable number of gate line sacrificial layer 105 / dielectric layer 106 pairs. In some embodiments, the total number of gate line sacrificial layer 105 / dielectric layer 106 pairs in the first stac...

Embodiment 2

[0171] This embodiment provides a three-dimensional NAND storage device structure, which can be prepared by the preparation method of the first embodiment above, but is not limited to the preparation method described in the first embodiment, as long as the device structure can be formed. For the beneficial effects achieved by the device structure, please refer to Embodiment 1, which will not be described in detail below.

[0172] like Figure 25 As shown, the structure includes:

[0173] The substrate layer 200 has opposite front and back sides;

[0174] The fourth stacked structure 201 and the fifth stacked structure 202 stacked in sequence are located on the front side of the substrate layer 200, wherein the fourth stacked structure 201 and the fifth stacked structure 202 include a gate layer 203 / dielectric layer 204 pair, the gate layer 203 includes the storage gate layer of the storage transistor and the upper selection gate layer of the upper selection transistor;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com