Manufacturing method of shield gate trench power device

A technology of power devices and manufacturing methods, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve problems such as electrical failure, abnormal morphology of polysilicon etching back, and damage to charge balance, so as to improve the appearance, Improve device performance, improve the effect of device electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

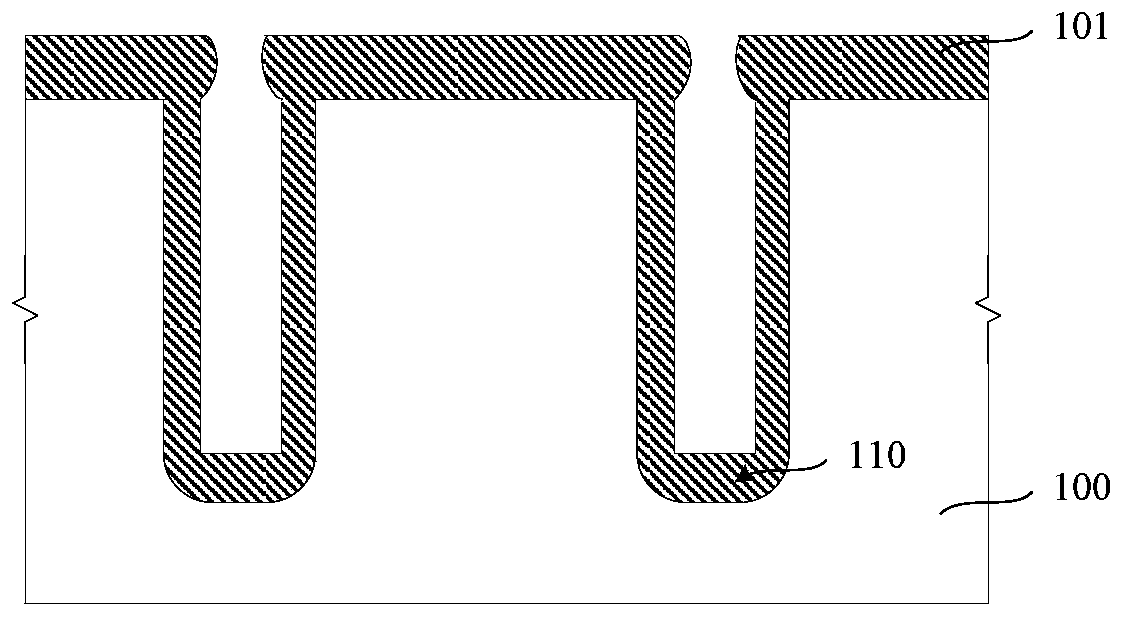

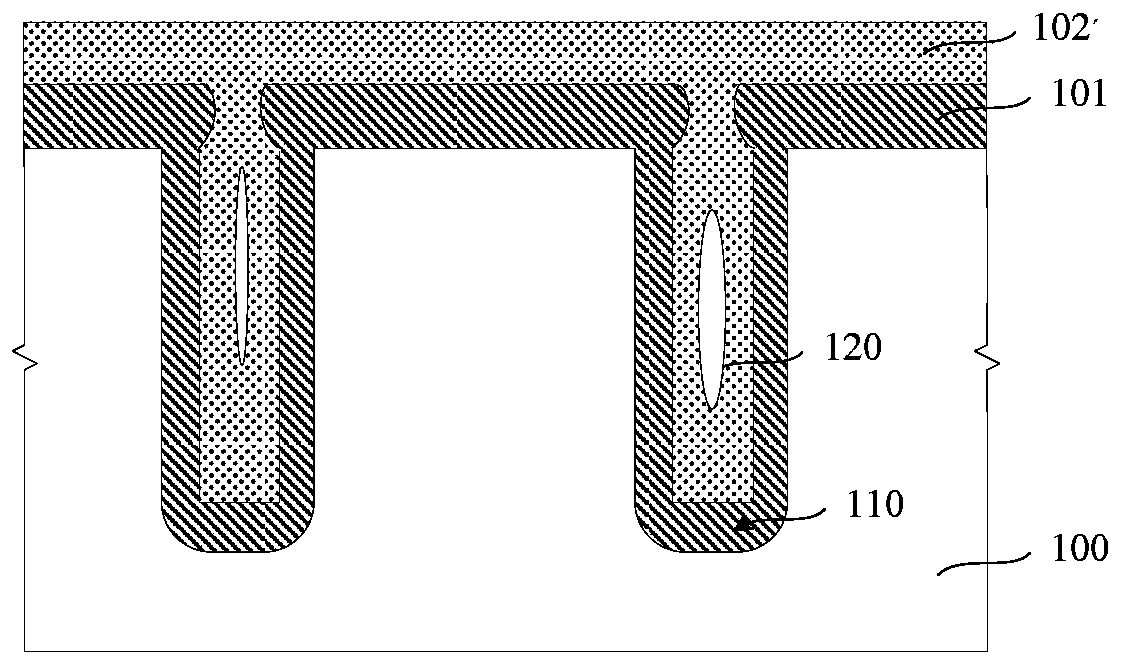

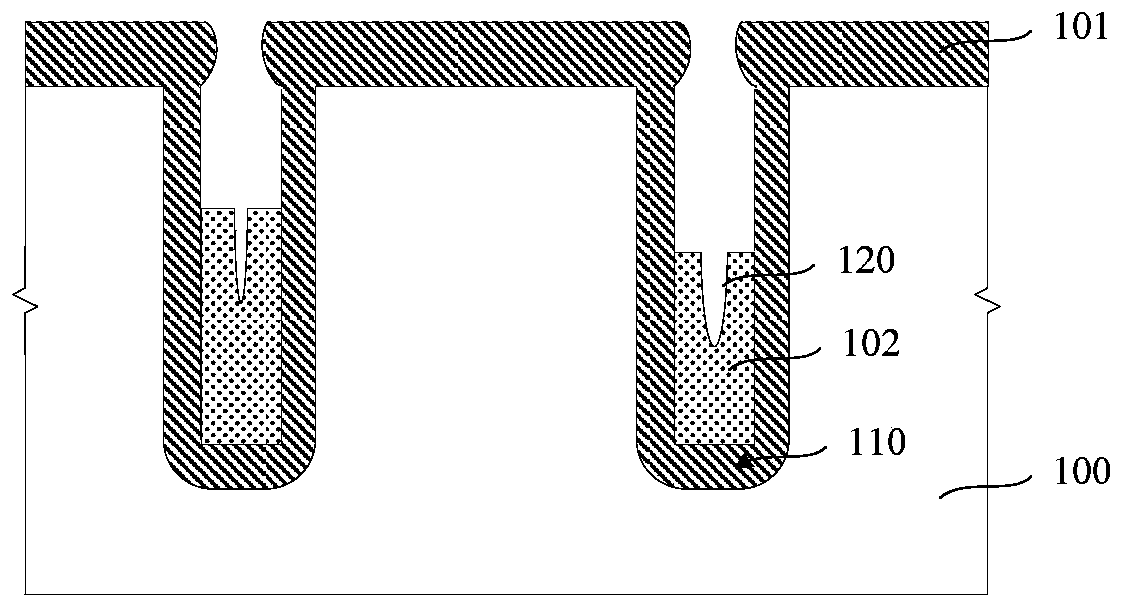

[0035] Figure 1A to Figure 1C It is a structural schematic diagram corresponding to corresponding steps of a manufacturing method of a shielded gate trench power device.

[0036] First, refer to Figure 1A As shown, a trench 110 is formed on a substrate 100 , a dielectric layer 101 is formed at the bottom and sidewalls of the trench 110 , and the dielectric layer 102 extends to cover the surface of the substrate 100 . The dielectric layer 101 is formed in two steps of a thermal oxidation method and a CVD process. Due to the characteristics of the CVD process, the dielectric layer on the surface of the substrate 100 extends toward the center of the trench 110, so that the width of the top of the trench 110 is smaller than that in the middle. and the width of the bottom form the “closed” shape of the trench 110 .

[0037] Next, refer to Figure 1B As shown, the trench 110 is filled with a shielding gate material layer 102 ′, and the shielding gate material layer 102 ′ extends...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com