Addressing method and module applied to on-chip control system and on-chip control system

An on-chip control and addressing module technology, applied in memory systems, memory address/allocation/relocation, instruments, etc., can solve problems such as information flow access bottlenecks, improve addressing efficiency and stability, and have high management flexibility Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

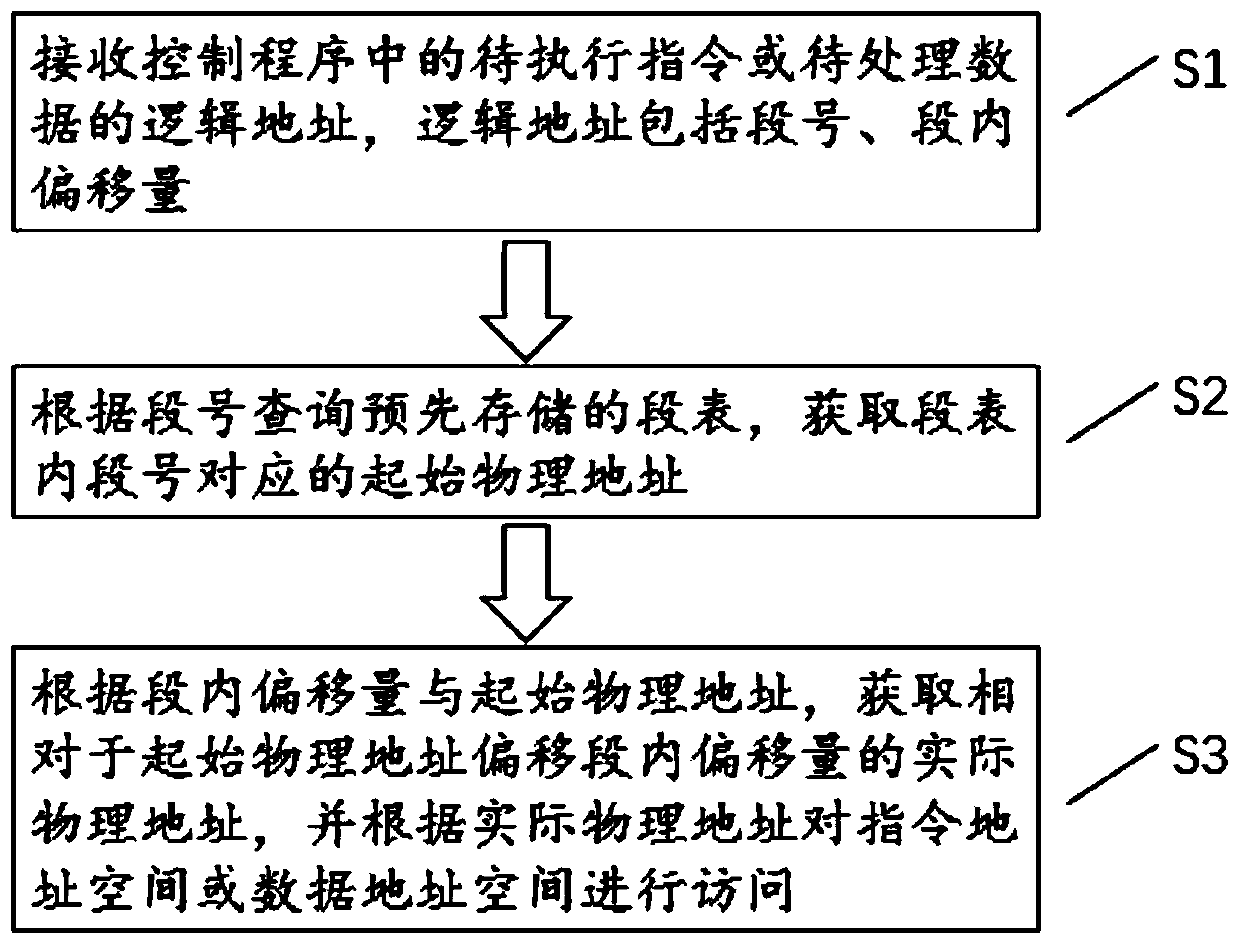

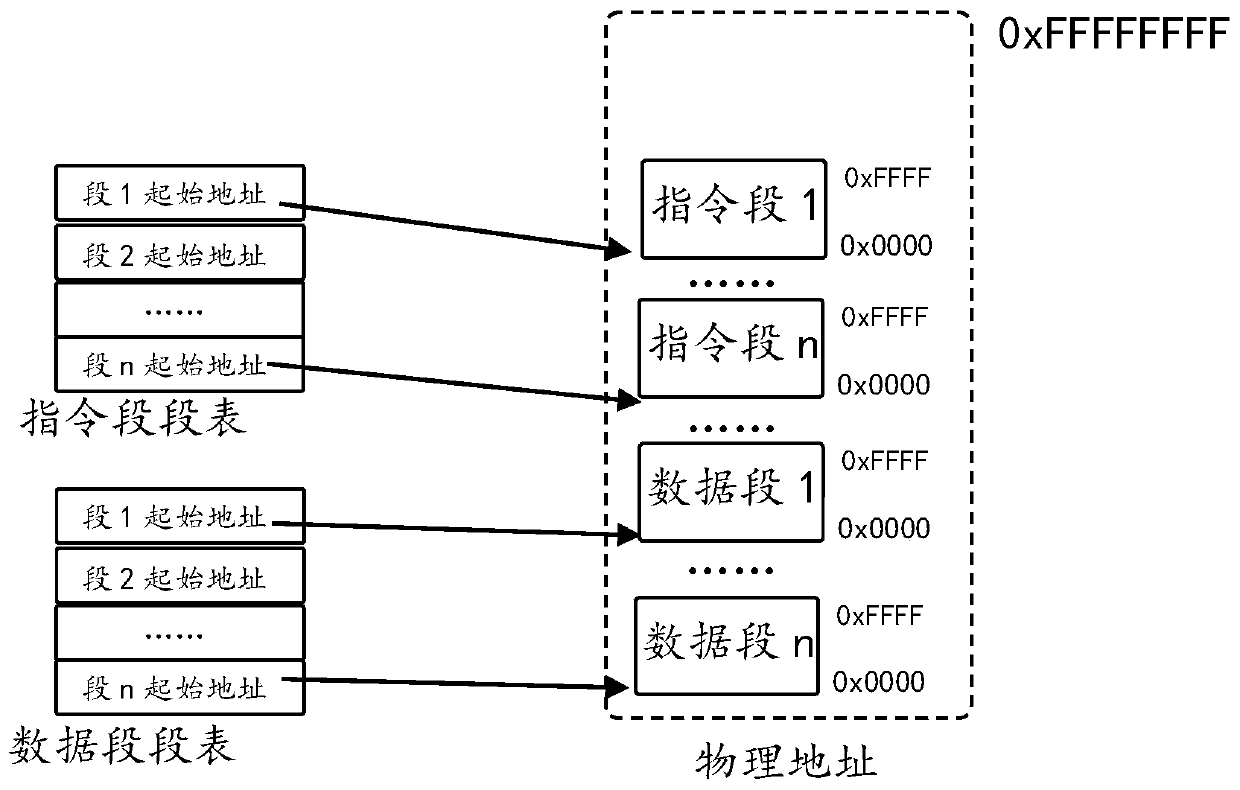

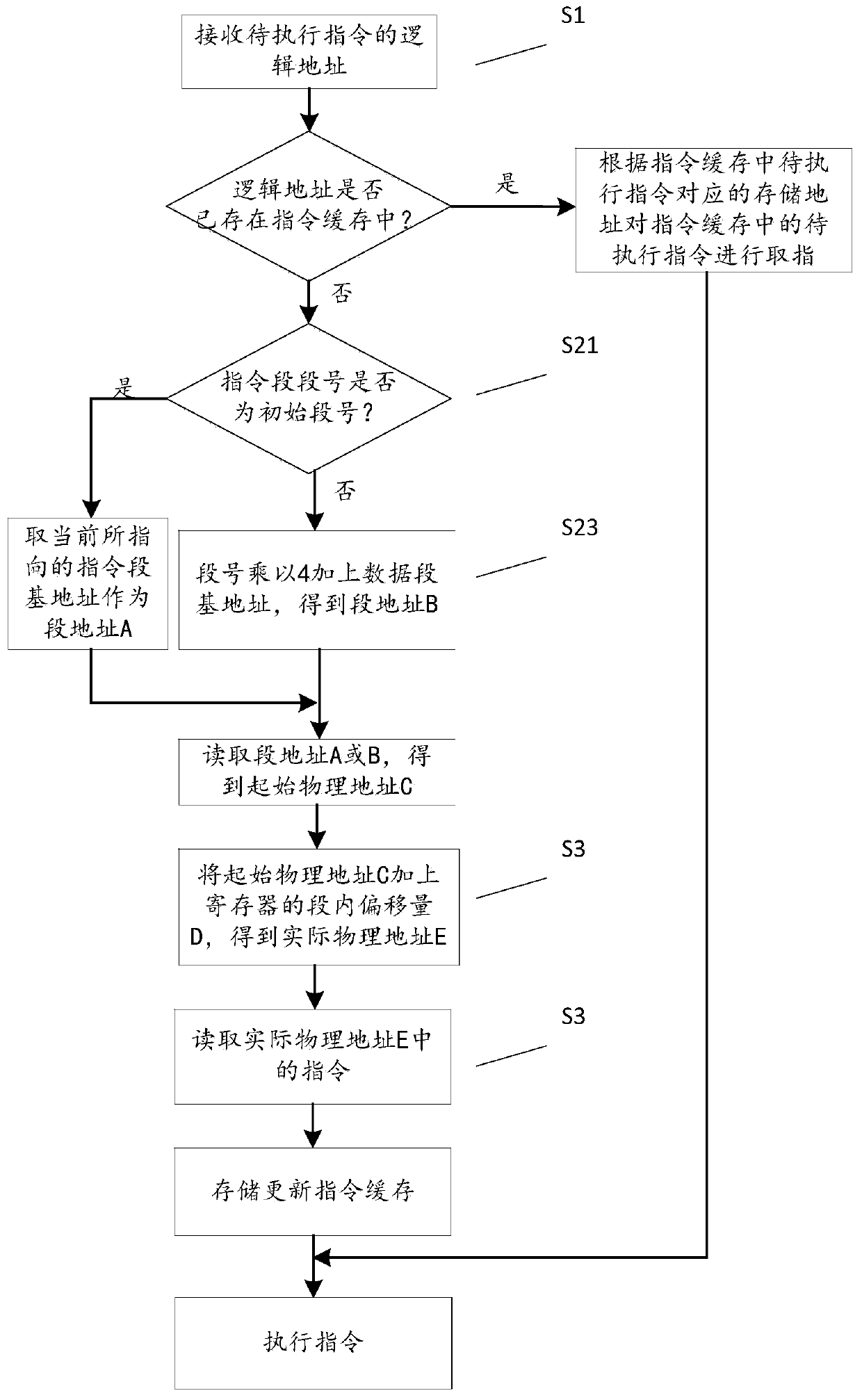

[0049] see figure 1 , the application provides an addressing method applied to an on-chip control system. The on-chip control system includes a central processing unit, a control program processor, and a memory. The central processing unit directly addresses the memory through a real physical address, and part of the address space of the memory It is configured to store the instruction address space of the instruction segment and the data address space of the data segment, and control the program processor to address the instruction address space or the data address space through the address translation of the logical address, including the following steps:

[0050] S1: Receive the logical address of the instruction to be executed or the data to be processed in the control program. The logical address includes the segment number and the offset within the segment;

[0051] S2: Query the pre-stored segment table according to the segment number, and obtain the starting physical a...

Embodiment 2

[0068] see Figure 6 , the present application provides an addressing module 100 applied to an on-chip control system based on Embodiment 1. The control program processor applied to the on-chip control system addresses the instruction address space or data address space of the memory, including:

[0069] The receiving sub-module 101 is used to receive the logical address of the instruction to be executed or the data to be processed in the control program, and the logical address includes a segment number and an offset within the segment;

[0070] Address conversion sub-module 102, address conversion sub-module 102 is pre-stored with a segment table storing the initial physical addresses of each instruction segment and data segment, address conversion sub-module 102 is used to query the segment table according to the segment number, and obtain the segment number in the segment table The corresponding starting physical address, and according to the offset in the segment and the ...

Embodiment 3

[0083] see Figure 7 and Figure 8 , the present application provides an on-chip control system, including a central processing unit 1, a control program processor 2, a memory 3, and an addressing module 100 based on Embodiment 2, wherein the addressing module 100 is located in the control program processor 2 (eg Figure 7 shown) or hang on the on-chip bus 4 of the on-chip control system as an independent IP core (such as Figure 8 As shown), the central processing unit 1 directly addresses the memory 3 based on the real physical address, and the control program processor 2 addresses the instruction address space or the data address space of the memory 3 through the addressing module 100 based on the logical address.

[0084] see Figure 7 In this embodiment, the addressing module 100 is set in the control program processor as an example to describe this embodiment in detail, but it is not limited thereto.

[0085] The addressing module of this embodiment is connected to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com