A kind of heterojunction bipolar transistor and its preparation method

A heterojunction bipolar and transistor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of high production cost, restrictions on SiGeHBT development and technology transformation, and long process development cycle, etc., to reduce Development and production costs, reduced collector width, and reduced parasitic effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] Hereinafter, embodiments of the present invention will be described with reference to the drawings.

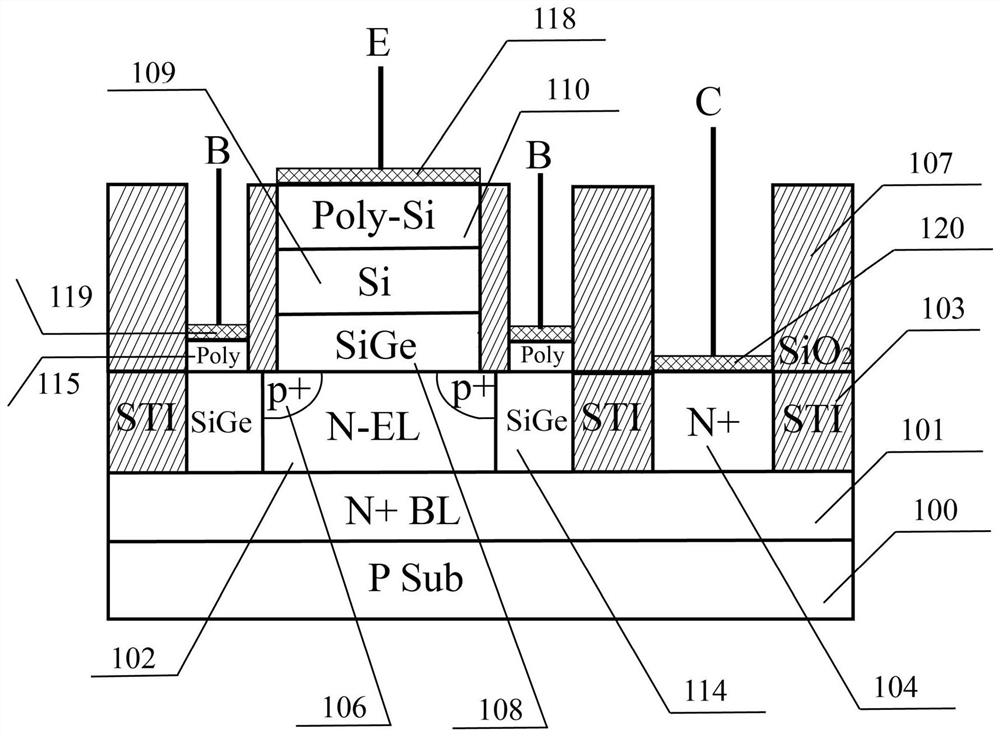

[0052] Such as figure 1 As shown, the heterojunction bipolar transistor of the present invention selects a P-type doped single-crystal Si substrate whose crystal orientation is (110); epitaxy a layer of N+ doped single-crystal Si layer on the substrate as a buried layer ; A layer of N-doped single crystal Si layer is epitaxially deposited on the surface of the buried layer as the collector area; three STI structures with a thickness of 400nm are formed in the collector area to realize the isolation of the collector and the base, and the collector N+ doping is performed on the right side of the region; ion implantation is performed on the N-doped collector region, and P+ doping is formed on both sides as an extrinsic base region; a layer with a thickness of 1-2 μm is deposited on the device surface SiO 2 layer to define the position of the active region; selectively ep...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com