Time domain finite difference method hardware accelerator architecture and implementation method thereof

A technology of finite difference in time domain and hardware accelerator, which is applied to architectures, instruments, and digital computer components with a single central processing unit. and other problems, to achieve the effect of correct function, play off-chip storage bandwidth capacity, and improve utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

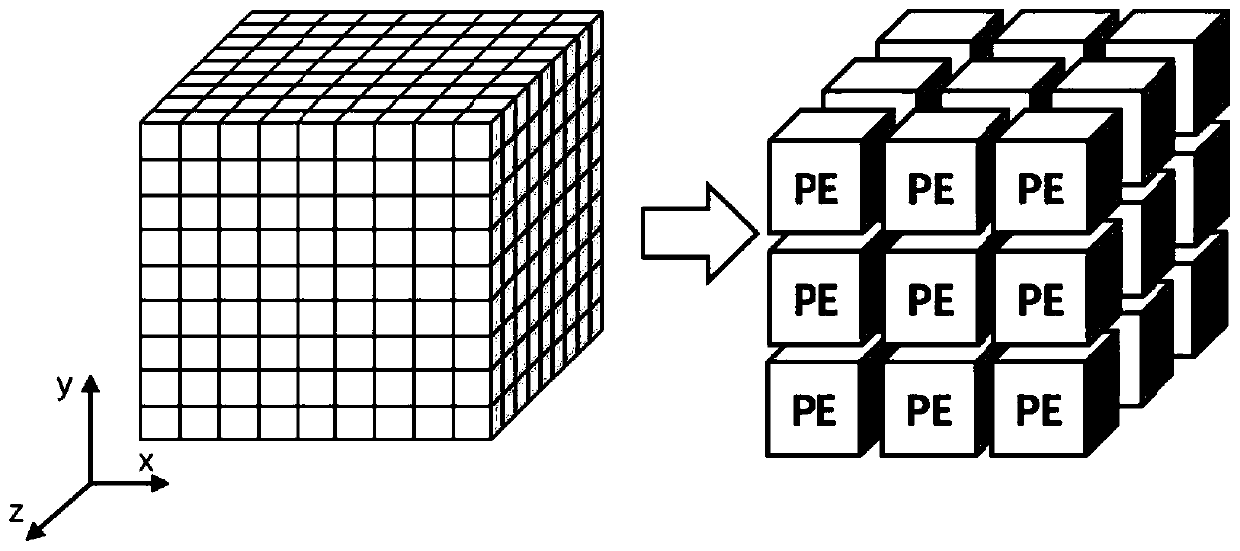

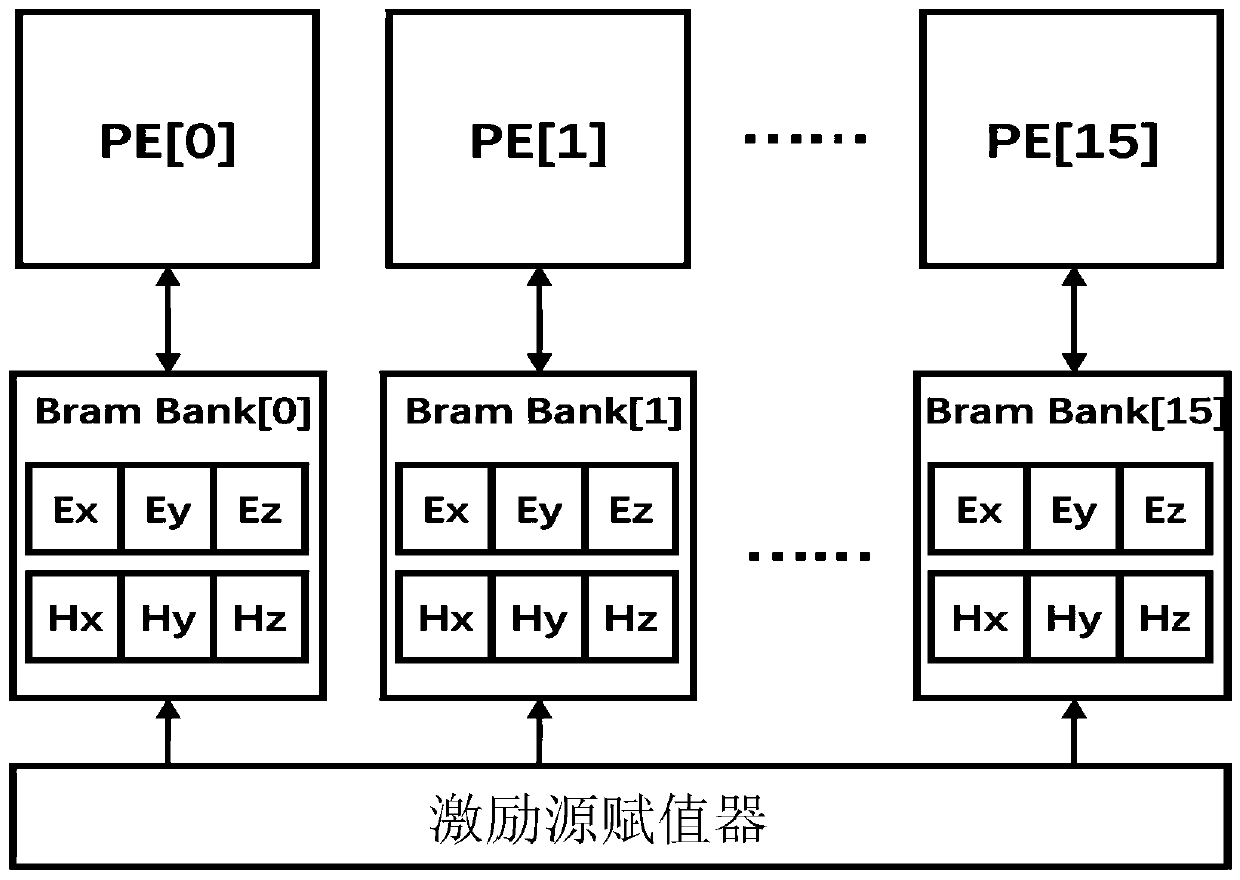

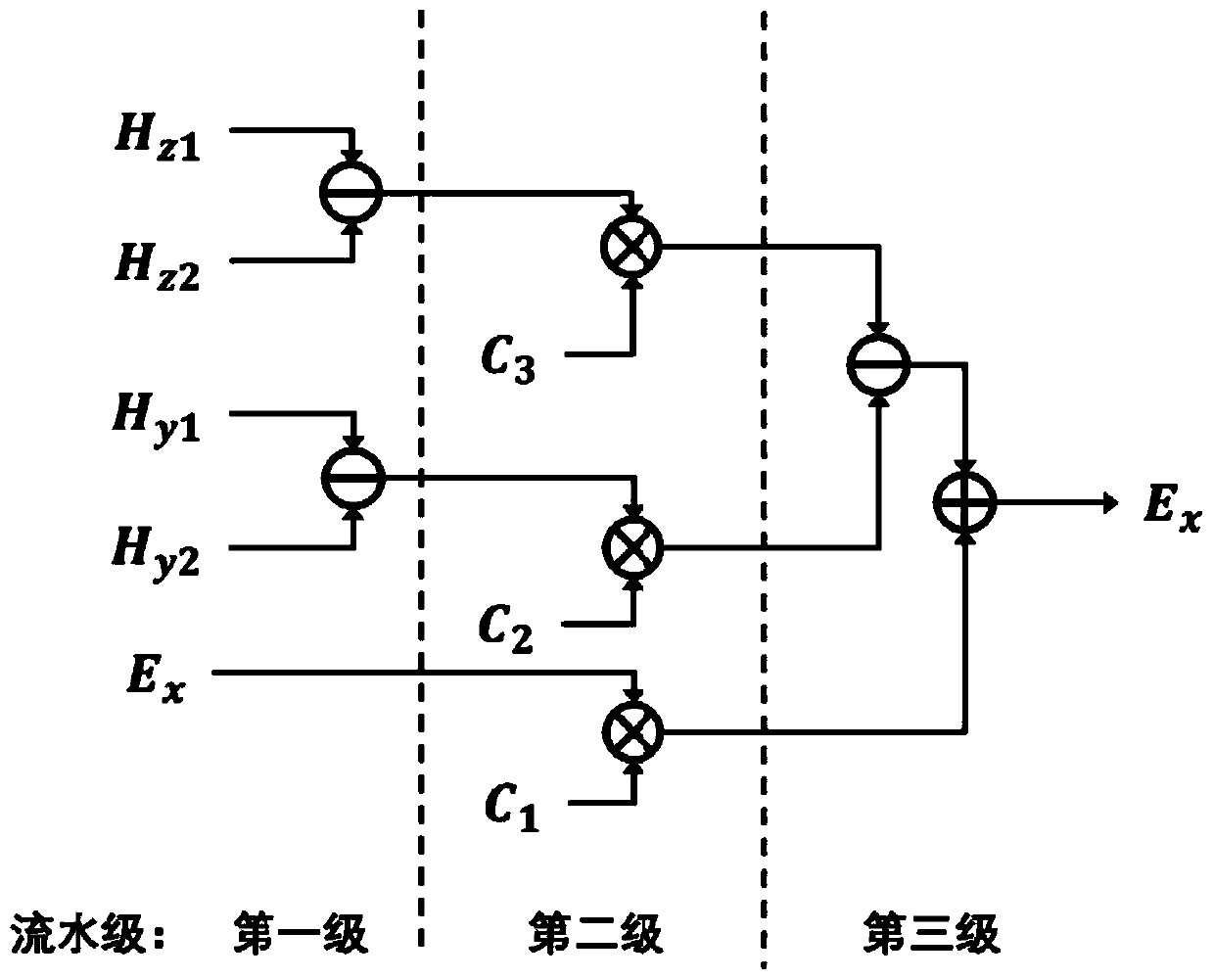

[0041] Such as figure 1 As shown, when the existing FDTD hardware accelerator based on the FPGA (Field Programmable Gate Array) platform calculates the electromagnetic field in the three-dimensional space, the large grid that needs to be simulated will be based on the logical resources and storage resources on the FPGA. The number of small grids is evenly divided into several small grids, and each small grid is allocated a computing processing unit PE (Processing Element) and a set of BRAM (Block RAM) for storing data, forming a three-dimensional array of small grids . Each PE is responsible for calculating the electric field value and magnetic field value of all grid points in the small grid, and updating the value of each grid point in turn by scanning. After all the small grids are calculated, the electric field value and magnetic field value in the small grid BRAM are output according to the combination of small grids to restore the structure of the large grid.

[0042]W...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com