Power semiconductor device cell structure, preparation method thereof and power semiconductor device

A technology for power semiconductors and devices, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

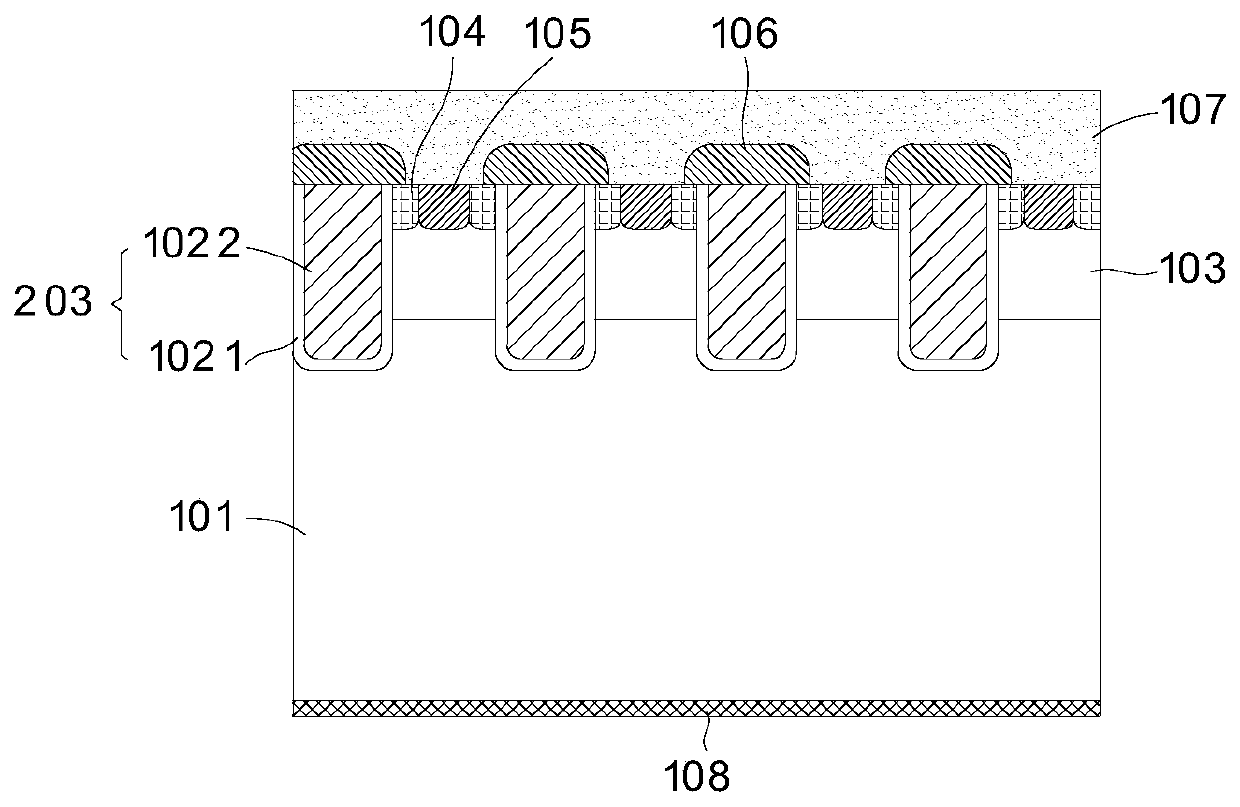

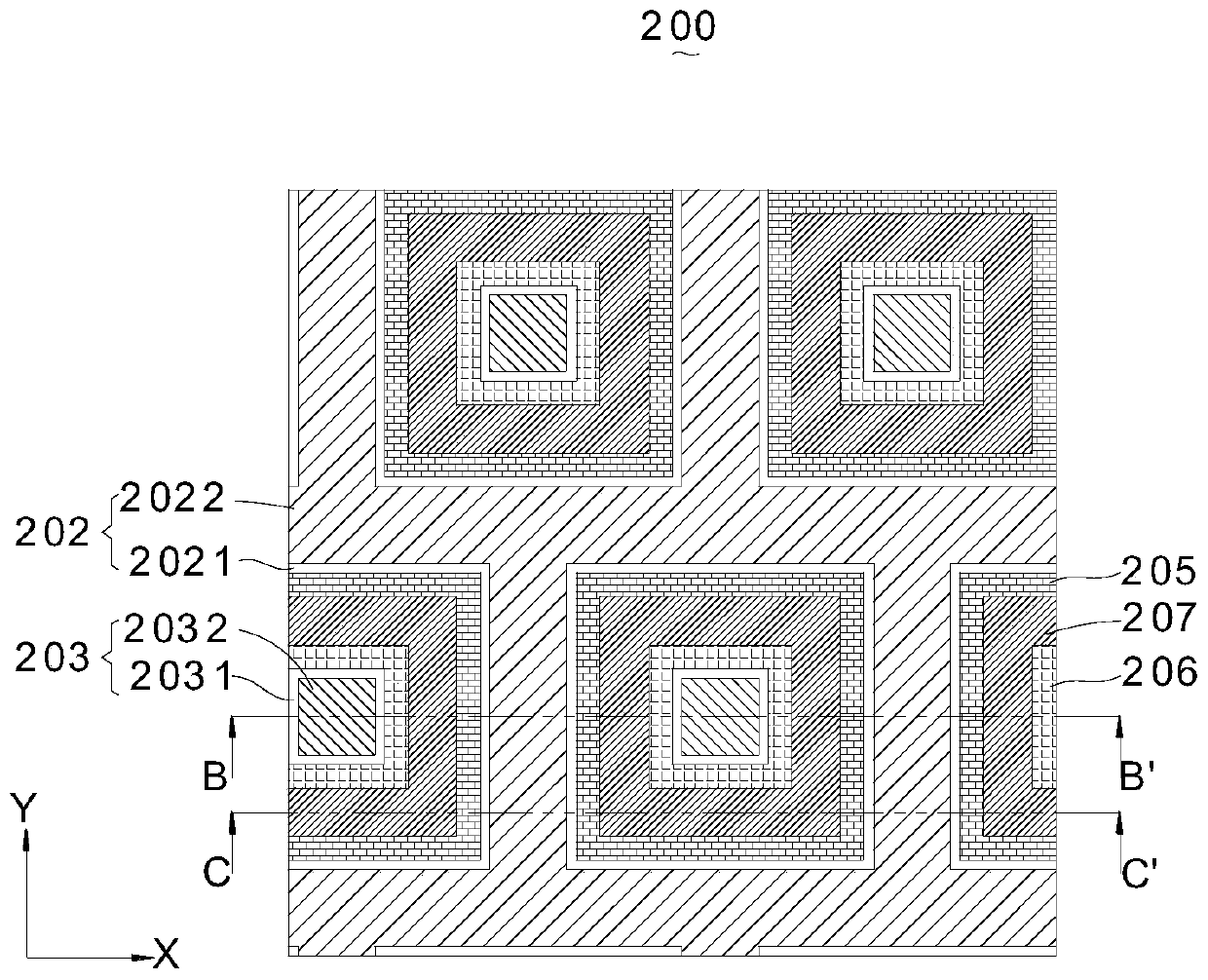

[0054] Such as Figure 3 to Figure 6 As shown, the embodiment of the present disclosure provides a power semiconductor device cell structure 200, including a substrate 201, a first trench gate 202, a second trench gate 203, a well region 204, a first source region 205, a second source region Region 206 , third source region 207 , first interlayer dielectric layer 208 , second interlayer dielectric layer 209 , emitter metal layer 210 and collector metal layer 211 .

[0055] It should be noted that, in order to image 3 with Image 6 The shapes and positions of the first trench gate 202, the second trench gate 203, the well region 204, the first source region 205, the second source region 206 and the third source region 207 are clearly shown in the figure, image 3 with Image 6 The substrate 201 , the first interlayer dielectric layer 208 , the second interlayer dielectric layer 209 , the emitter metal layer 210 and the collector metal layer 211 are not shown. but combine ...

Embodiment 2

[0075] On the basis of the first embodiment, this embodiment provides a method for preparing the cell structure 200 of a power semiconductor device. Image 6 It is a schematic flowchart of a method for preparing a power semiconductor device cell structure 200 shown in an embodiment of the present disclosure. Figure 7-Figure 12 It is a schematic cross-sectional structure formed by the relevant steps of a method for preparing a cell structure 200 of a power semiconductor device shown in an embodiment of the present disclosure. Below, refer to Figure 7 with Figure 8-Figure 13 The detailed steps of an exemplary method of the method for manufacturing the power semiconductor device cellular structure 200 proposed by the embodiment of the present disclosure will be described.

[0076] Such as Figure 7 As shown, the preparation method of the power semiconductor device cellular structure 200 in this embodiment includes the following steps:

[0077] Step S101 : providing a first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com