Processing method of wafer

A processing method and wafer technology, applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of shortening the processing time, reducing the spacer, and spending the processing time, so as to shorten the processing time, reduce the The effect of spacer, efficient fracture

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

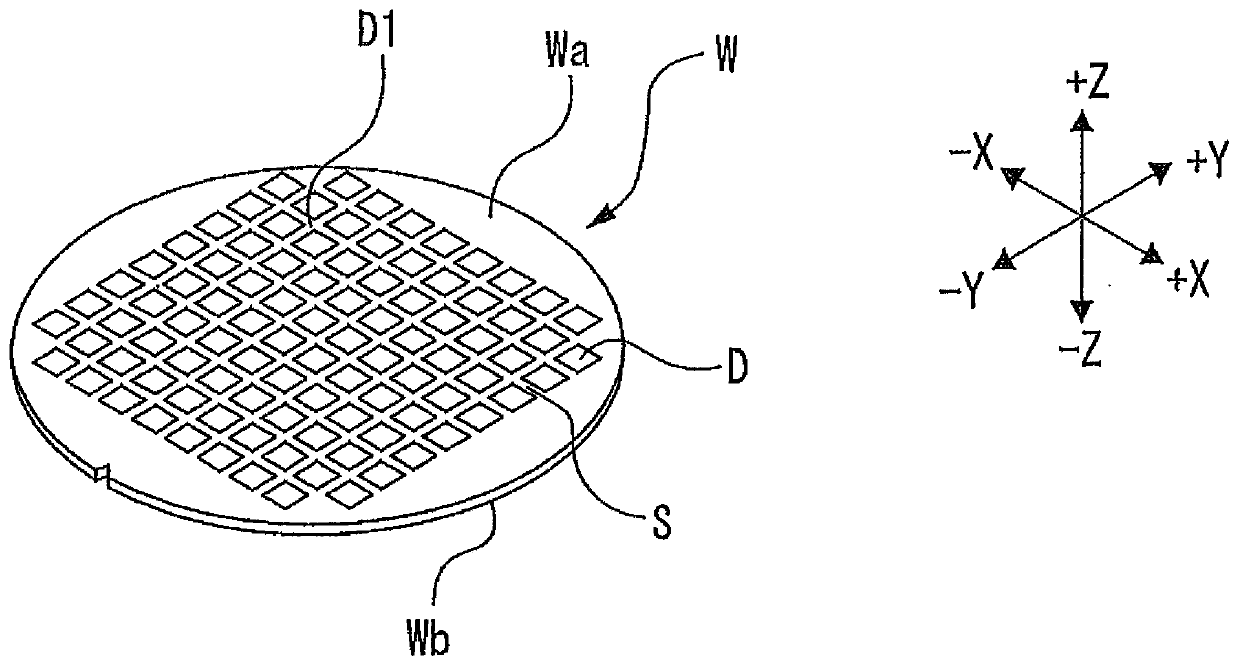

[0038] Hereinafter, the wafer processing method of the present invention (the processing method of the first embodiment) will be described figure 1 Each step of the processing method when the illustrated wafer W is divided into chips having devices D will be described.

[0039] The wafer W is, for example, a semiconductor wafer with a circular outer shape using silicon as a base material. Its front surface Wa is divided into a grid by a plurality of vertical dividing lines S, and ICs and other devices are formed in each area divided into the grid. D. In addition, for example, a device layer D1 is laminated on the planned dividing line S. The device layer D1 includes a circuit layer made of metal and an insulating layer (for example, a low-k film) that insulates the circuits.

[0040] In addition to silicon, the wafer W may also be made of gallium arsenide, sapphire, gallium nitride, silicon carbide, or the like.

[0041] (1) Piece pasting steps

[0042] In the wafer processing method...

Embodiment approach 2

[0115] Hereinafter, the wafer processing method (the processing method of Embodiment 2) implementing the present invention will be described figure 1 Each step of the processing method when the illustrated wafer W is divided into chips having devices D will be described.

[0116] (1-1) Application of water-soluble resin to the wafer in the wafer dividing step

[0117] In the wafer processing method of this embodiment 2, firstly figure 1 The wafer W shown is transported to Picture 11 The spin coater 4 shown. In addition, before being transferred to the spin coater 4, a protective tape (not shown) is attached to the front surface Wa of the wafer W. Then, the wafer W is sucked and held by the holding table 40 with the front Wa side to which the protective tape is pasted, and the holding table 40 holding the wafer W is lowered to the coating height position in the housing 44. In addition, the supply port 450 of the nozzle 45 is positioned above the center of the wafer W.

[0118] Next...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com