A design method of lithographic overlay marking

A design method and lithographic overlay technology, which are applied in optics, instruments, and photoplate-making processes on patterned surfaces, etc., can solve problems such as the inability to meet the compensation needs of lithography processes, and the inability to use high-order error compensation algorithms, etc., to achieve reflection Effects of process manufacturing error, improvement of chip manufacturing yield, improvement of feedback correction accuracy and overlay error compensation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

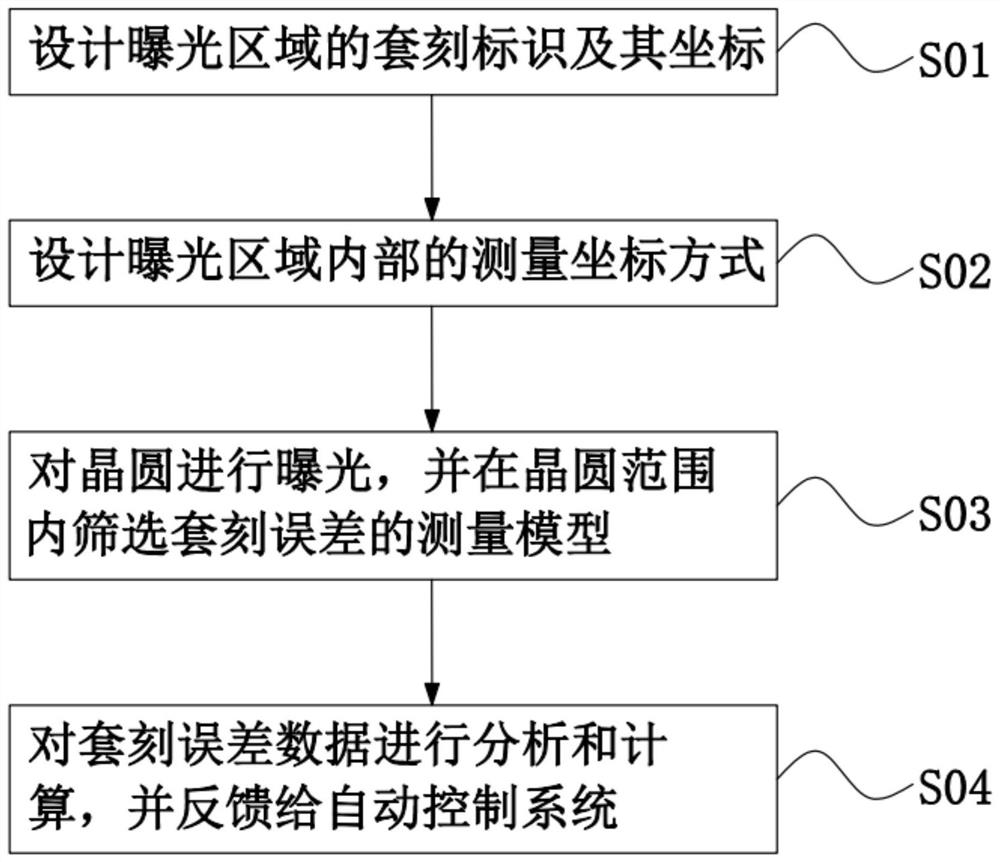

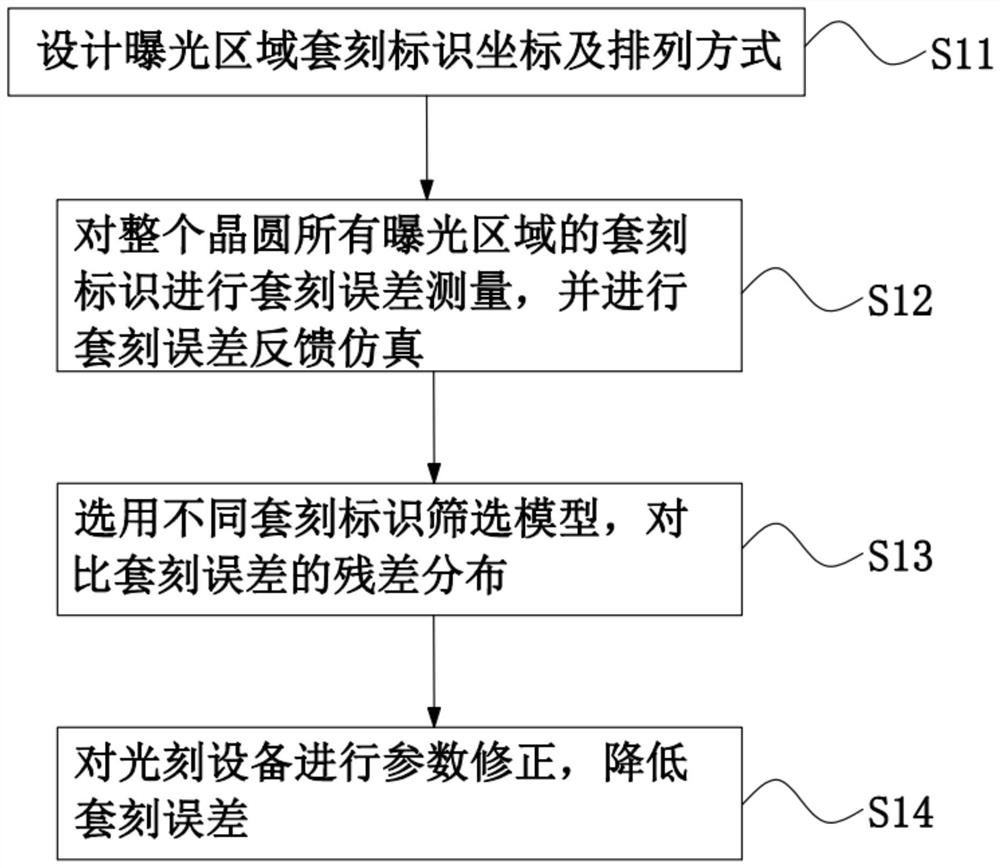

[0035] A method for designing a photolithographic overlay mark, comprising the steps of:

[0036] S01. Design the overlay marks and their coordinates inside the exposure area. There are no less than 10 overlay marks in each exposure area, and the coordinate design of the overlay marks evenly covers the entire exposure area;

[0037] S02. Design the measurement coordinate method inside the exposure area, and measure the coordinates through two design methods: the complementary point selection method and the comprehensive point selection method;

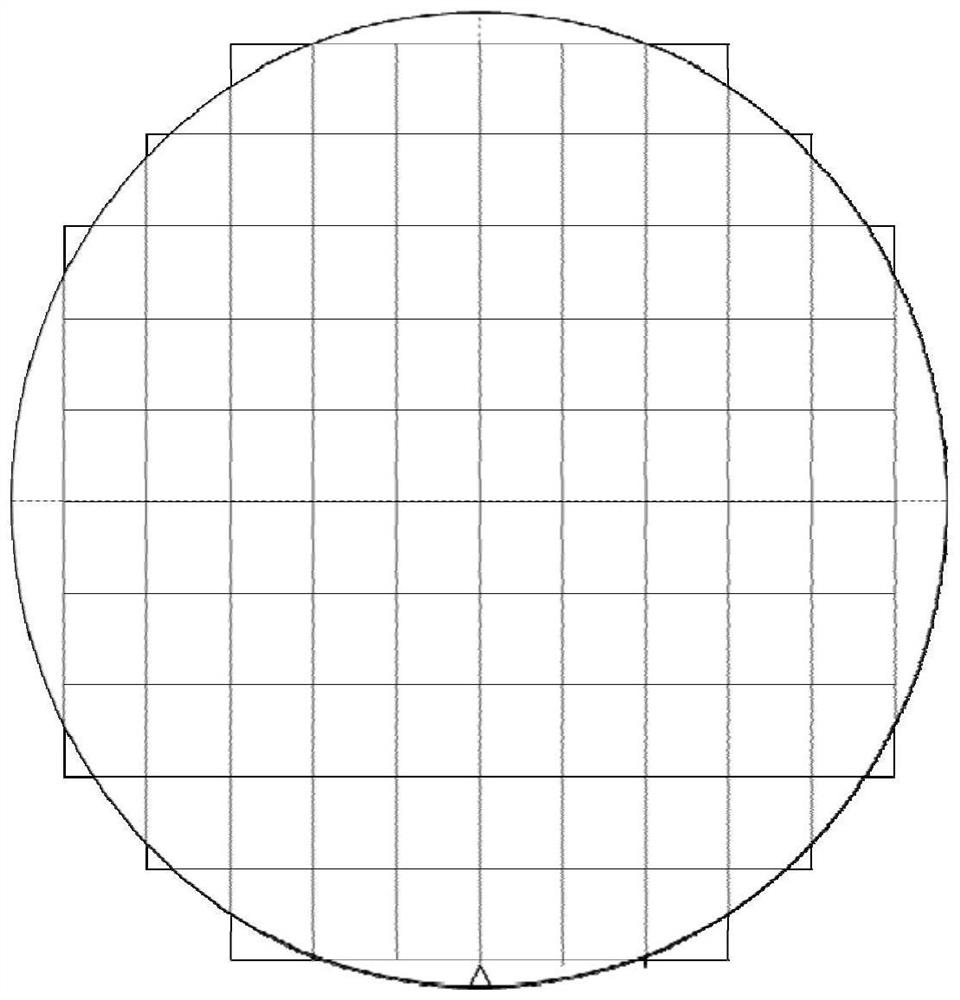

[0038] S03. Expose the wafer, and screen the measurement model of the overlay error within the wafer range. In the wafer coordinate system, mark all the exposure areas according to the horizontal and vertical directions, and optimize the exposure area according to the actual process characteristics. Carry out overlay error measurement;

[0039] S04. Analyze and calculate the overlay error data, and feed it back to the automatic contro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com