Double-phase coefficient adjustable analog multiplication calculation circuit for convolutional neural network

A convolutional neural network and analog multiplication technology, which is applied in the field of digital-analog hybrid integrated circuits and dual-phase coefficient adjustable analog multiplication calculation circuits, to achieve high linearity, reduce signal routing, good linearity and mismatching effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The present invention is further illustrated below in conjunction with specific embodiments, should be understood that these embodiments are only used to illustrate the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand the various equivalent forms of the present invention All modifications fall within the scope defined by the appended claims of this application.

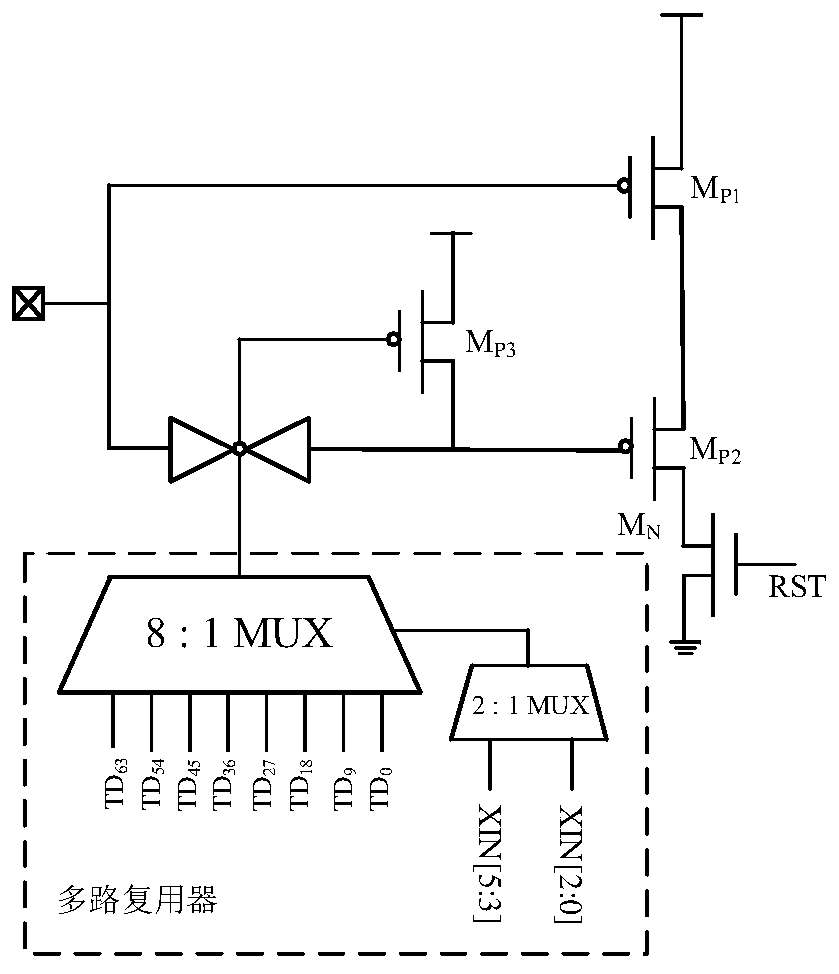

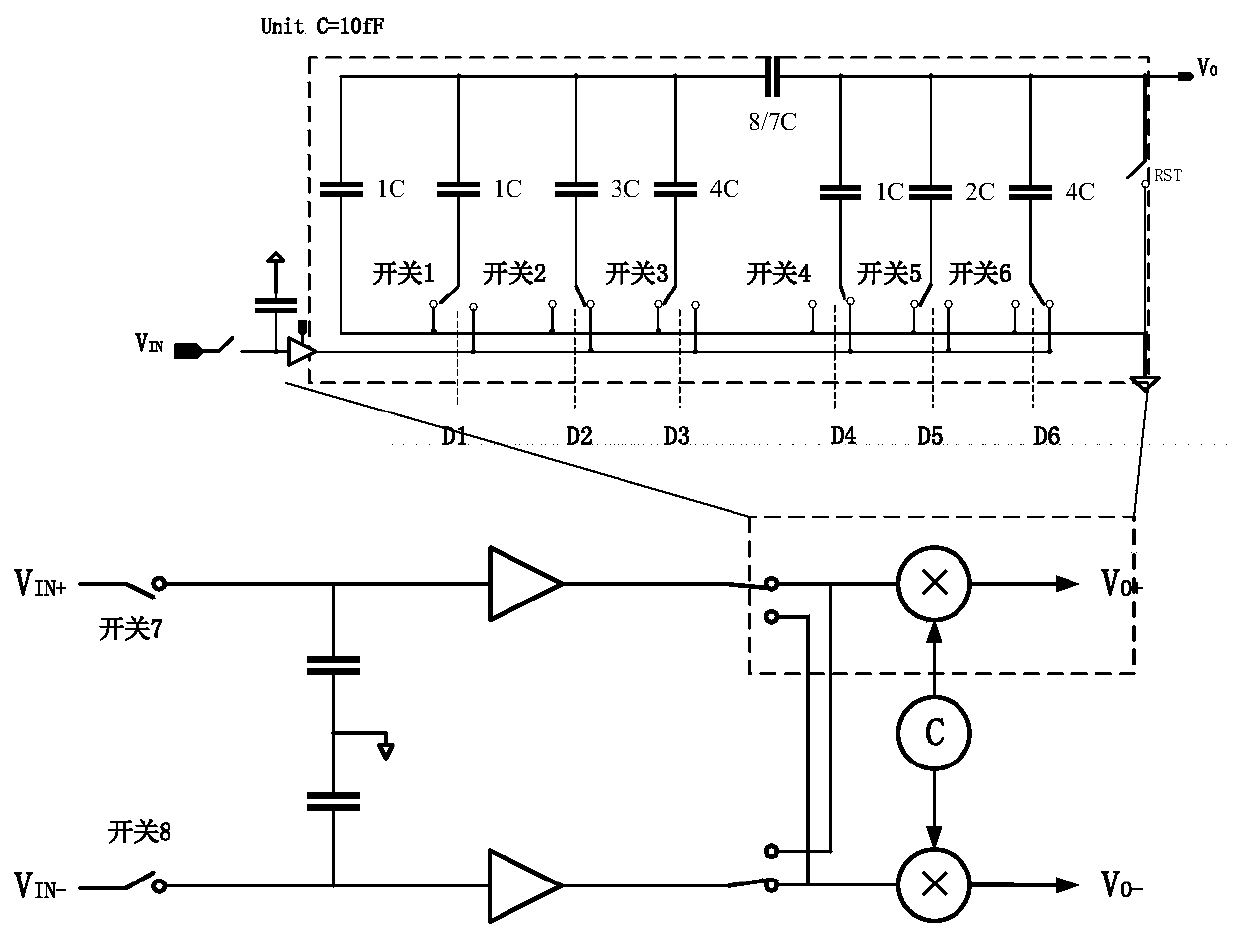

[0015] The bi-phase coefficient adjustable analog multiplication calculation circuit for convolutional neural network performs deep convolution, pointwise convolution, activation layer, pooling layer and batch normalization in the neural network under the control and scheduling of internal modules multiplication in the layer. Such as figure 1 As shown, the neural network-oriented dual-phase coefficient-adjustable analog multiplier includes: a current-type network digital-to-analog conversion mod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com