Trench MOSFET integrated with ESD protection and manufacturing method thereof

An ESD protection and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electrical components, diodes, etc., can solve the problems of increasing the clamping voltage and impedance of the energy discharge channel, increasing the difficulty of the process, and poor process stability, achieving The effect of stable ESD discharge characteristics, stable ESD protection ability and good ESD protection ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

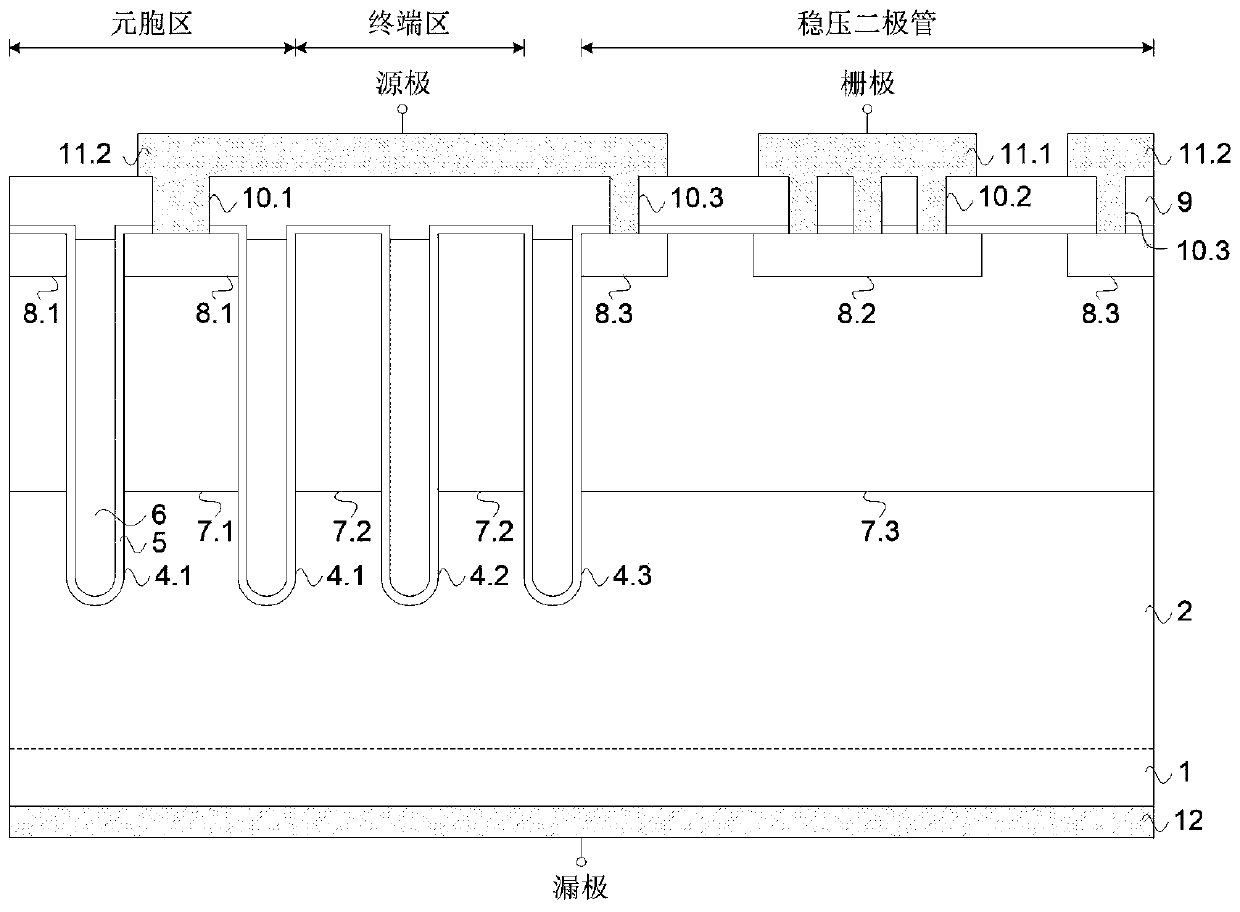

[0080] Embodiment 1: A trench MOSFET with integrated ESD protection, see figure 2 , image 3 .

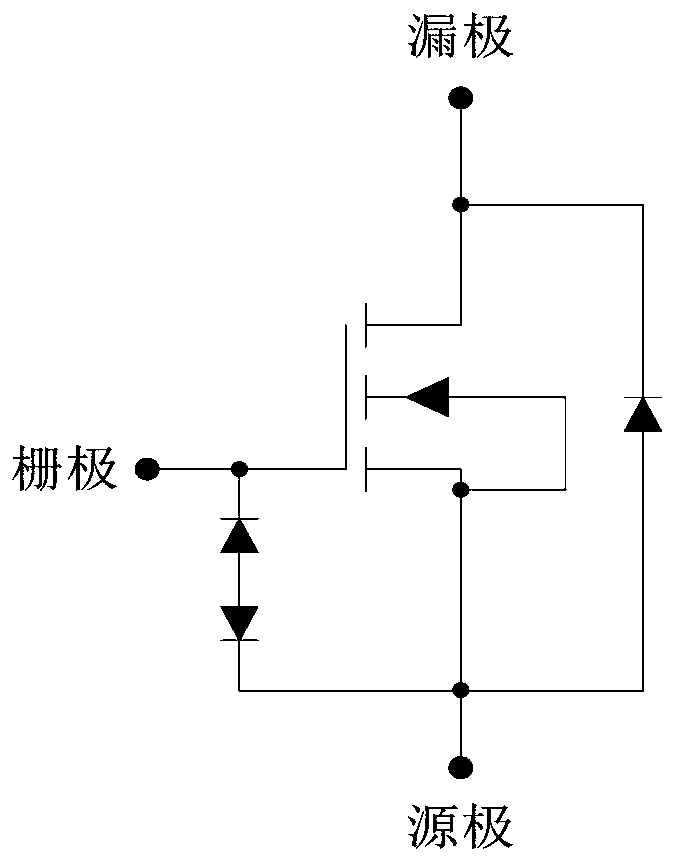

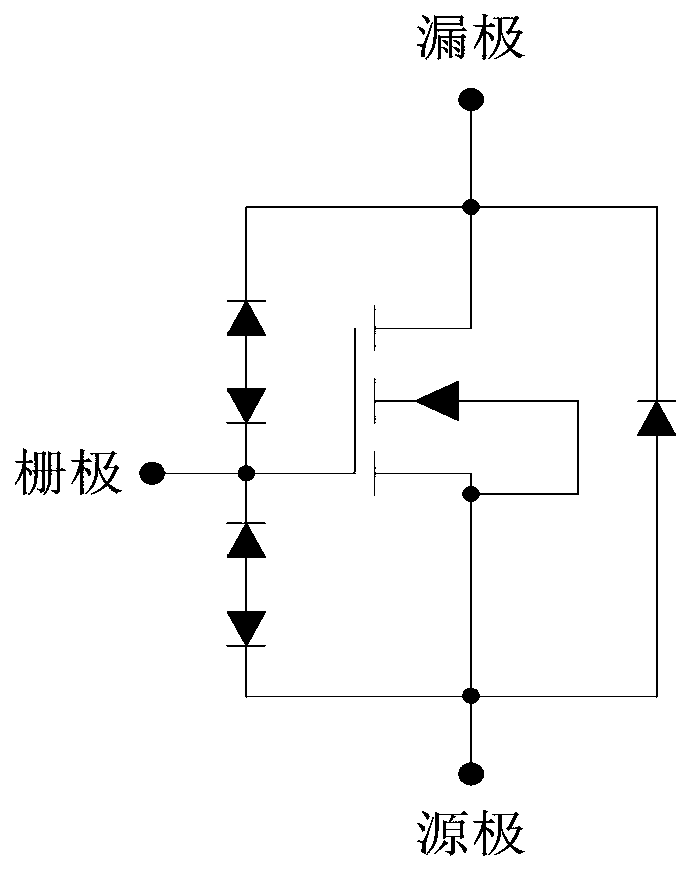

[0081] The trench MOSFET of integrated ESD protection of the present invention, can refer to figure 2 Between the gate and the source of the MOSFET, there is a Zener diode composed of forward and reverse PN junctions connected in series, one end of the Zener diode is connected to the gate of the MOSFET, and the other end is connected to the source of the MOSFET; Between the gate and the drain of the gate, there is a Zener diode composed of forward and reverse PN junctions connected in series, one end of the Zener diode is connected to the gate of the MOSFET, and the other end is connected to the drain of the MOSFET; the Zener diode Both are body silicon diodes, and their equivalent circuit diagrams are shown in image 3 shown.

[0082] Such as figure 2 As shown, the Zener diode is located under the gate of the MOSFET and the surrounding area of the gate. Between the Zener...

Embodiment 2

[0095] Example 2, see Figure 4 to Figure 12 , a method for manufacturing a trench MOSFET with integrated ESD protection, which is used to manufacture the trench MOSFET with integrated ESD protection described in Example 1, and the trench MOSFET with integrated ESD protection described in Example 1 is suitable for N Type trench MOSFET and P-type trench MOSFET, for ease of understanding and description, this embodiment takes the manufacturing method of N-type trench MOSFET as an example for illustration, specifically it includes the following steps:

[0096] S1. Form a lightly doped N-type epitaxial layer 2 on the upper surface of a heavily doped N-type silicon substrate 1, see Figure 4 .

[0097] S2, forming a hard mask 3 on the upper surface of the N-type epitaxial layer 2, the material of the hard mask 3 is silicon oxide or silicon nitride, or a stacked layer formed of silicon oxide and silicon nitride, the hard mask 3 has a thickness of 200-600nm, see Figure 5 .

[00...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com