ZYNQ FPGA chip, data processing method thereof and storage medium

A data processing and chip technology, applied in the direction of electrical digital data processing, general-purpose stored program computer, architecture with a single central processing unit, etc., can solve the problem of affecting the overall performance of the processing deep learning model, occupying data transmission time, frequent data interaction, etc. problem, achieve high real-time response processing delay, low processing delay, and improve processing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

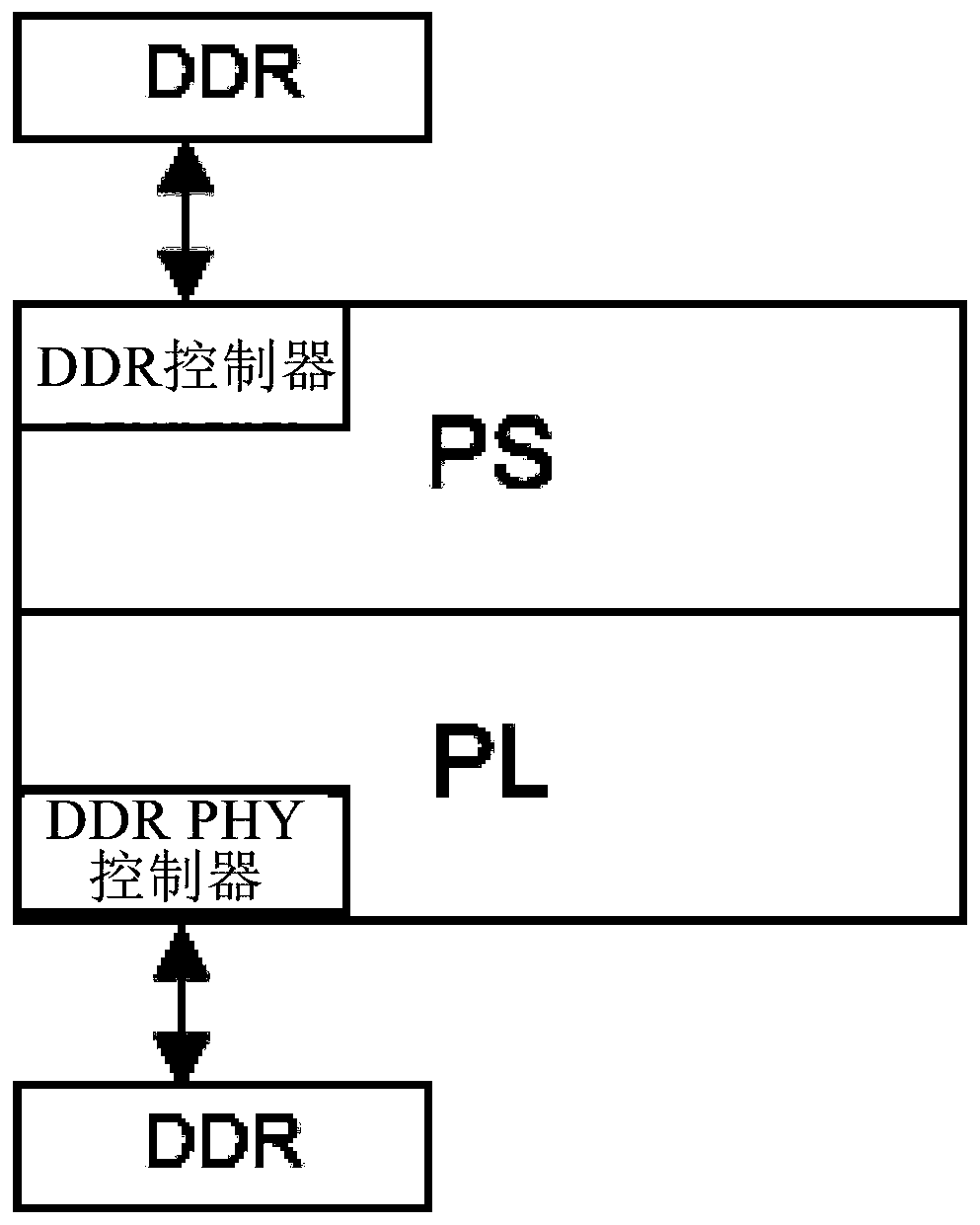

[0053] figure 1 It is a schematic diagram of the hardware structure of the existing deep learning model based on the ZYNQ FPGA chip. refer to figure 1 , mount the DDR on the PS part and the PL part respectively, where the PS part realizes data communication with the DDR mounted on it through its built-in DDR controller, and the PL part operates other supporting DDR PHY controllers and the DDR mounted on it through the user interface Realize data communication.

[0054] According to the processing characteristics of the deep learning model, based on the above hardware solution, the switching of data between the PS part and the PL part causes frequent data interaction between the DDRs on both sides and takes up data transmission time, thus affecting the overall performance of the deep learning model.

[0055] Moreover, since the existing ZYNQ FPGA chip supports up to 4 DDR particles, based on the consideration that the parallelism of DDR particles affects the bandwidth, the DD...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com