Comparator and analog-to-digital converter

A technology of comparators and latches, applied in analog-to-digital converters, analog-to-digital conversion, code conversion, etc., can solve the problems of large noise and offset, reduce reset speed, increase power consumption, etc., and achieve low noise requirements, Effect of suppressing noise and increasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

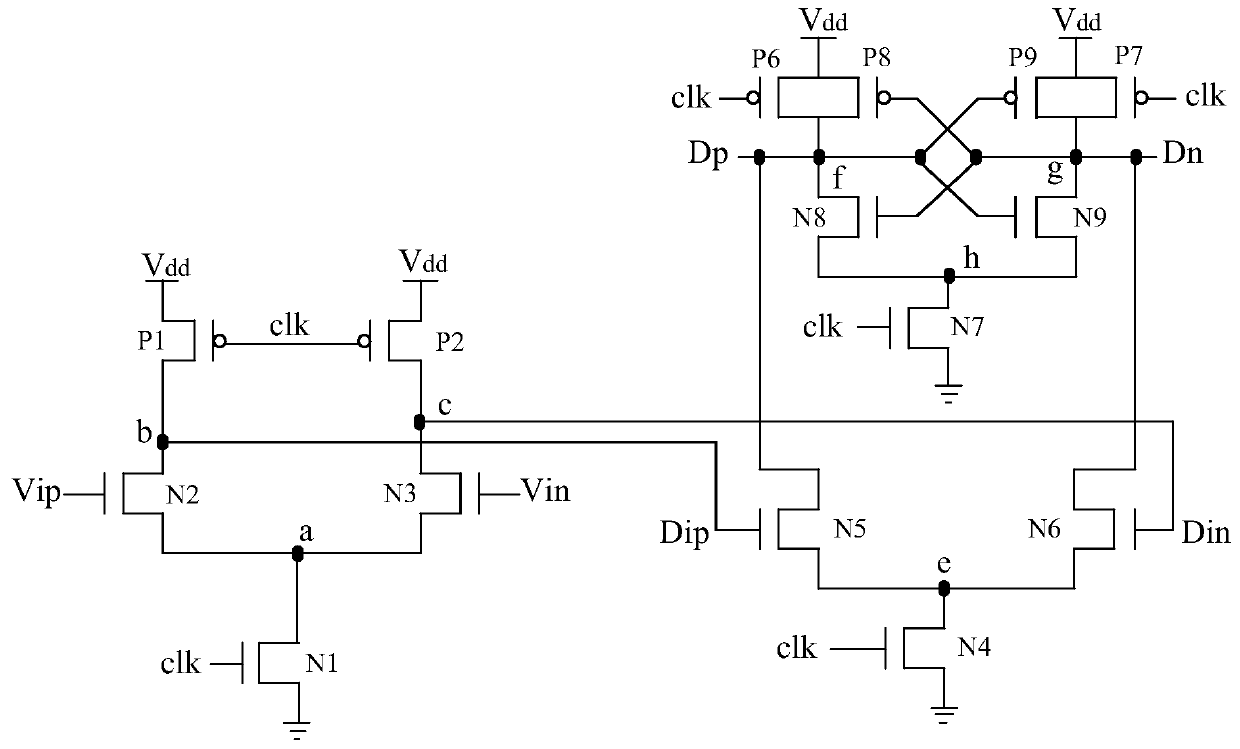

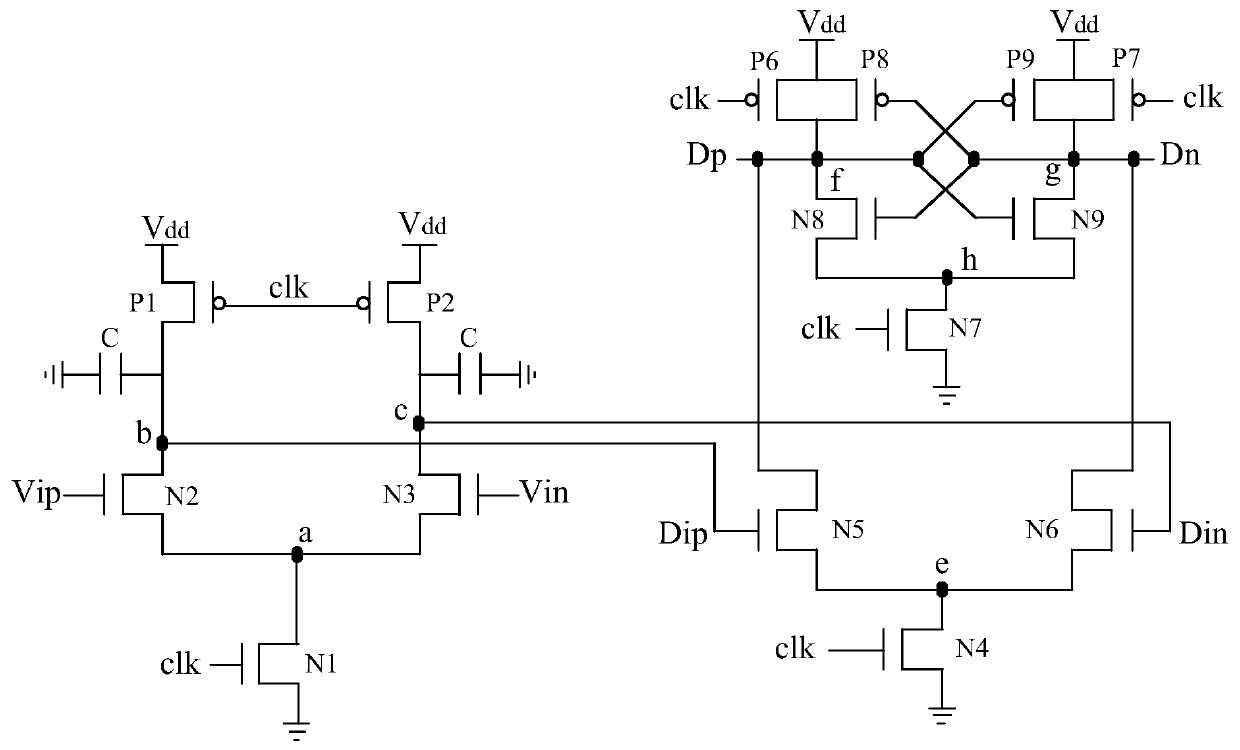

[0138] An embodiment of the present invention provides a comparator, such as Figure 4 As shown, it includes a pre-amplification stage and a latch, and the first input signal Vip and the second input signal Vin are amplified by the pre-amplification stage and input to the latch;

[0139] The pre-amplification stage includes a pre-amplification stage main unit, a pre-amplification stage gain bootstrap unit, and a load capacitance adjustment unit; the input terminal of the pre-amplification stage main unit is connected to the first input signal Vip and the second input signal Vin, and the The main unit of the pre-amplification stage amplifies the first input signal Vip and the second input signal Vin, and the output terminals of the main unit of the pre-amplification stage (at the second node b and the third node c) are connected to the input of the latch end; the pre-amplification stage gain bootstrap unit is connected to the output of the pre-amplification stage main unit to f...

Embodiment 2

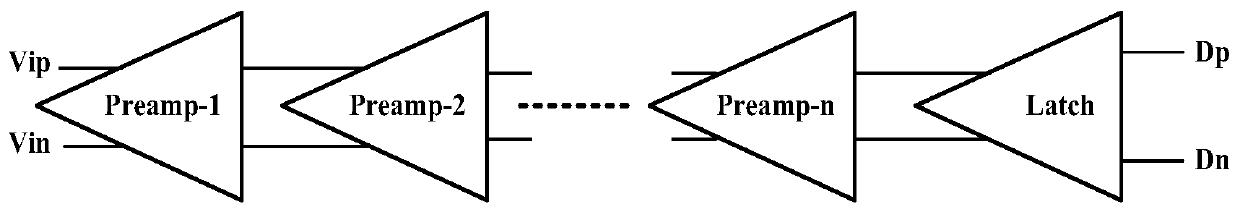

[0159] The comparator formed by one-stage pre-amplification stage and one-stage latch is a basic comparator, and commonly used high-precision comparators are generally composed of multi-stage pre-amplification stages and one-stage latch. Therefore, the embodiment of the present invention propose a comparator such as Figure 9 As shown, the comparator includes a multi-stage pre-amplification stage and a first-stage latch, and the structure of each stage pre-amplification stage and the latch is the same as in Embodiment 1, and the input of the pre-amplification stage main unit in the first stage pre-amplification stage The first input signal Vip and the second input signal Vin are connected, the main units of the pre-amplification stage in the multi-stage pre-amplification stage are cascaded, and the output of the main unit of the pre-amplification stage in the last pre-amplification stage is connected to the input of the latch end.

[0160] In detail, such as Figure 9 As sho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com