Array substrate and manufacturing method thereof, display panel and display module

A technology for array substrates and display panels, applied in the fields of array substrates and their manufacture, display panels and display modules, can solve the problems of reducing the pull-out force test of the single-layer area width and the difficulty of COF pull-out force guarantee, and achieve increased Effect of pulling force and increasing contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

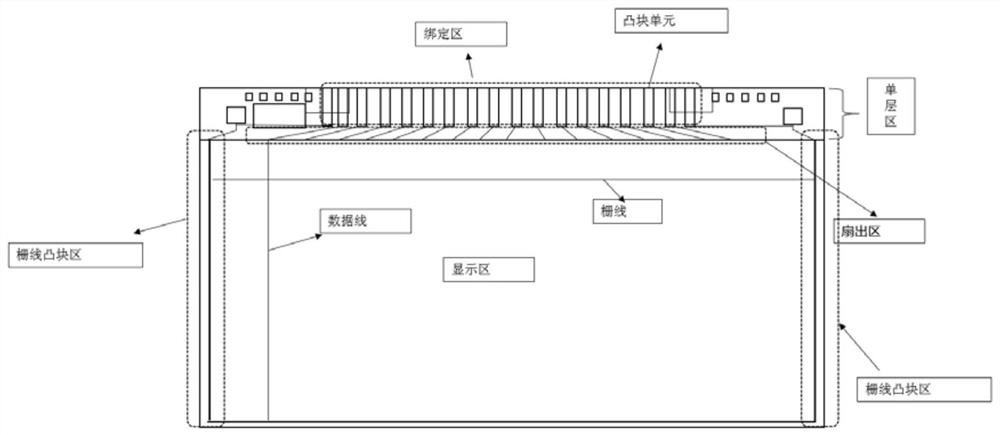

[0038] see figure 1 The array substrate provided by the first embodiment of the present invention includes a display area, a fan-out area (Fan-out) located on one side of the display area, a single-layer area located outside the fan-out area, and a single-layer area located between the display area and the single-layer area. side gate line bump area. The single-layer area is further divided into binding areas. Wherein, the data line and the gate line are set in the display area; the bump unit is set in the binding area for binding with the circuit board. The circuit board is, for example, a Chip On Film (COF for short). A grid line bump is arranged in the grid line bump area, which is connected to the grid line and connected to the bump unit through the silver paste in the single layer area.

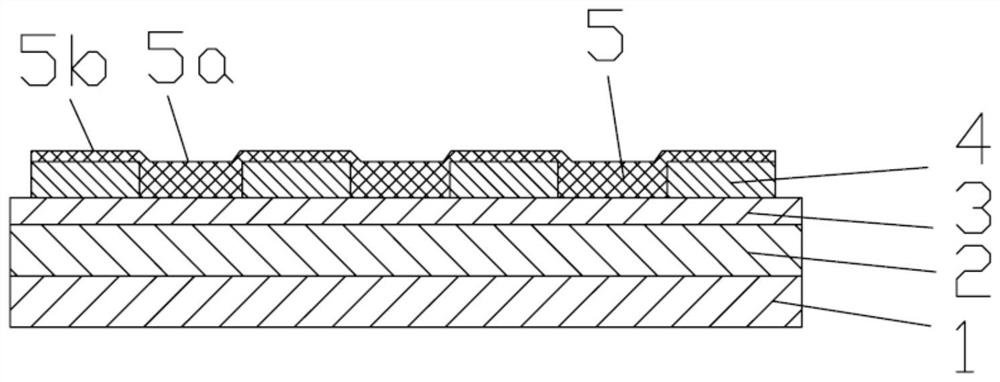

[0039] see figure 2 , the array substrate includes a glass substrate 1, a buffer layer 2 and a planar layer 3 sequentially arranged on the glass substrate 1, and the bump unit inclu...

no. 2 example

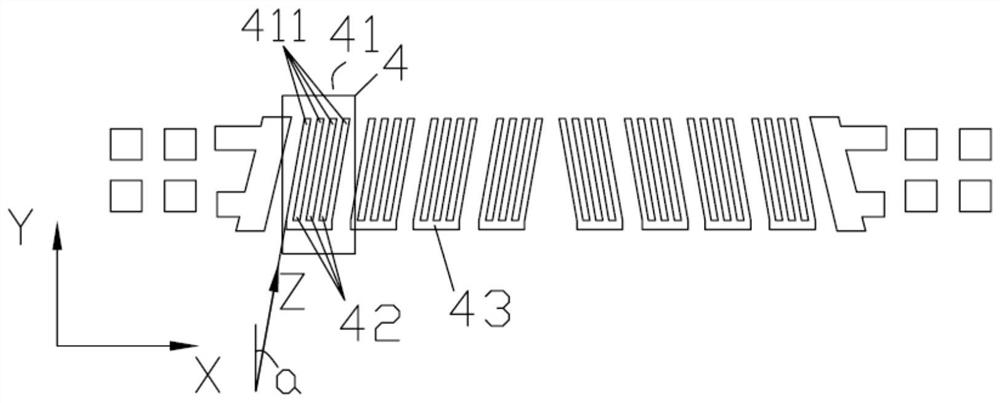

[0045] exist image 3 , in the Z direction, there is only one block 411, but the present invention is not limited thereto, such as Figure 4 As shown, the array substrate provided by the second embodiment of the present invention, compared with the above-mentioned first embodiment, also includes a bump unit, and only the differences between this embodiment and the above-mentioned first embodiment will be described in detail below.

[0046] Specifically, the bump unit includes a plurality of grid line bump layers 4' arranged at intervals along the X direction, and each grid line bump layer 4' includes a main body part 41' and a plurality of hollows arranged in the main body part 41'. Section 42'. The main body 41' includes a plurality of sub-blocks 411' arranged at intervals along the X direction and the Z direction, that is, the plurality of sub-blocks 411' are arranged in an array in the X direction and the Z direction, and two adjacent sub-blocks 411 'The space between con...

no. 3 example

[0049] Such as Figure 5 As shown, the array substrate provided by the third embodiment of the present invention, compared with the above-mentioned first and second embodiments, also includes bump units. The following only discusses the difference between this embodiment and the above-mentioned first and second embodiments. The differences are described in detail.

[0050] Specifically, the bump unit includes a plurality of grid line bump layers 4 ″ arranged at intervals along the X direction, and each grid line bump layer 4 ″ includes a main body 41 ″ and a plurality of hollows arranged in the main body 41 ″ Part 42". The main body part 41" includes a plurality of blocks 411" arranged at intervals along the Z direction, and the space between two adjacent blocks 411" forms a hollow part 42". Thus, in the Z direction, the gate The line bump layer 4" has a concave-convex structure, so that the surface of the data line bump layer 5 covering it and away from the gate line bump la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com