A convolutional neural network accelerator circuit based on a fast filtering algorithm

A convolutional neural network and filtering algorithm technology, applied in the field of convolutional neural network accelerator circuits, can solve problems such as reducing the utilization rate of computing units and consuming large hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The technical solutions in the embodiments of the present invention will be described clearly and in detail below with reference to the drawings in the embodiments of the present invention. The described embodiments are only some of the embodiments of the invention.

[0036] The technical scheme that the present invention solves the problems of the technologies described above is:

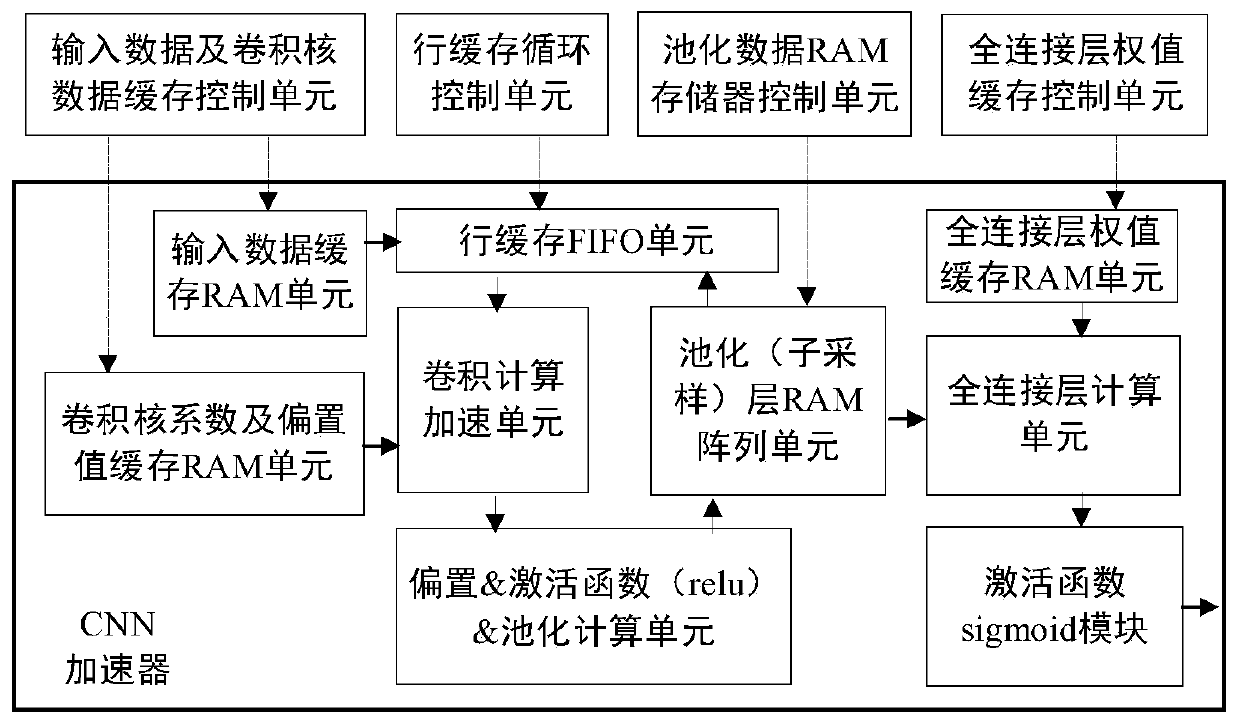

[0037] like figure 1 It is a system block diagram for implementing a convolutional neural network accelerator circuit provided by the present invention. This block diagram describes the layer-by-layer acceleration hardware architecture for implementing CNN on FPGA. The architecture does not design specific hardware for each layer. Instead, a set of hardware is designed and then reused in the different layers that need to be used, where the line cache loop control unit decides when to start each hardware unit. This architecture can realize the calculation of multiple layers in CNN with le...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com