A wafer level packaging method of an MEMS device

A technology of wafer-level packaging and devices, applied in semiconductor/solid-state device parts, piezoelectric/electrostrictive/magnetostrictive devices, instruments, etc., can solve the problems of increasing the damage probability of MEMS devices, and reach the optional range Wide, reduce the damage probability, reduce the effect of package cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

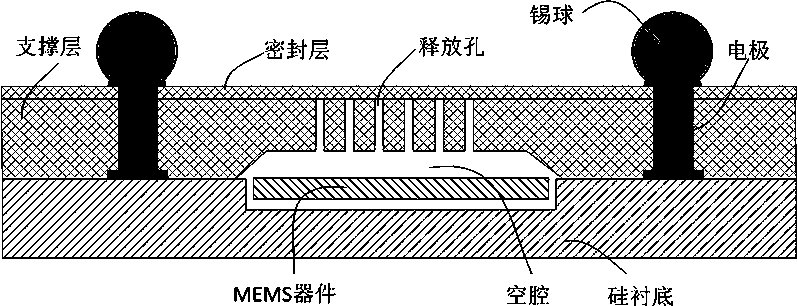

[0028] see Figure 4 , Embodiment 1 of the MEMS device wafer-level packaging method of the present application includes the following steps.

[0029] Step 401, such as Figure 5A As shown, a layer of temporary bonding material 102 is deposited on the carrier wafer 101 . Wafer 101 is a wafer for carrying a package structure, without MEMS devices thereon. Preferably, the carrier wafer 101 can be made of single crystal silicon, glass and other materials. Preferably, the temporary bonding material 102 is thermally sensitive, photosensitive, or easily corroded by chemicals, so that the packaging structure can be effectively peeled off from the carrier wafer 101 during subsequent processes. The deposition process is also called a deposition process, preferably chemical vapor deposition (CVD), physical vapor deposition (PVD), etc., and can also be in the form of spin coating or bonding.

[0030] Step 402, such as Figure 5B As shown, a first layer of polymer 103 for making a pac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com