An FPGA-based domestic platform database acceleration system and method

A technology for accelerating systems and databases, applied in database design/maintenance, structured data retrieval, architecture with a single central processing unit, etc., can solve problems such as high CPU power consumption, non-openness, and limited performance of independent CPUs, and achieve outstanding results Substantial features, reliable design principles, and the effect of improving execution efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

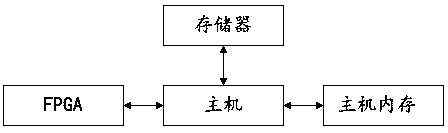

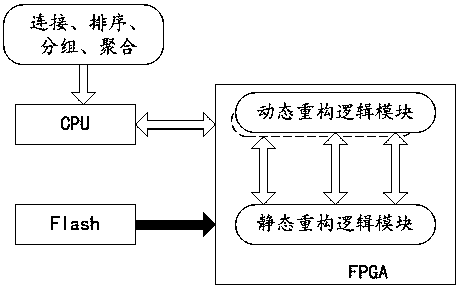

[0045] Such as Figure 1-2 As shown, a domestic platform database acceleration system based on FPGA includes a host and an FPGA board connected to the host, and the host includes a CPU, a PCIe driver, and a HOST program;

[0046] The FPGA board is connected to the CPU through the PCIe interface;

[0047] PCIe driver, used to establish the data transmission path between CPU and FPGA;

[0048] The HOST program is responsible for operation analysis and allocation, so that the CPU offloads computationally intensive tasks to the FPGA for execution;

[0049] The FPGA chip is used to offload the computationally intensive tasks from the CPU to perform operations;

[0050] The host also includes a Kernel.lib module and a runtime support library;

[0051] The Kernel.lib module is used to use the runtime support library to realize the distribution of parallel acceleration function files and algorithms.

[0052] The PCIE driver is responsible for establishing the data transmission pat...

Embodiment 2

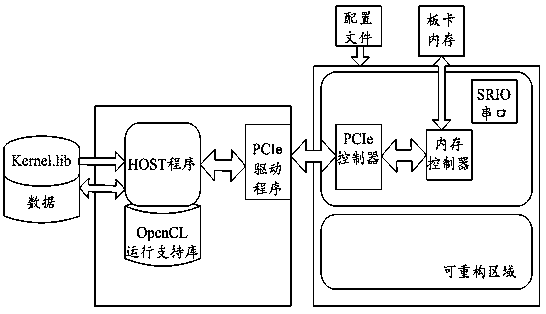

[0062] Such as image 3 As shown, the embodiment of the present invention provides a kind of FPGA-based domestic platform database acceleration method, comprises the following steps:

[0063] S1: The FPGA loads the configuration file of the statically reconfigured logic module, and cooperates with the PCIe driver to establish a data transmission path between the CPU and the FPGA;

[0064] S2: The host HOST program obtains platform and device information;

[0065] S3: The host HOST program establishes the running context according to the obtained information;

[0066] S4: Copy the data of the established running context to the memory of the board; in this step, the data is copied to the memory of the board through the data path established in step S1.

[0067] S5: The files in the Kernel.lib module are sent to the dynamic reconfigurable logic module in the FPGA, and the data in the memory of the board enters the dynamic reconfigurable logic module. The data is based on the ac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com