On-chip detection system and test method for identifying aged and recycled integrated circuit

An on-chip detection and integrated circuit technology, which is applied in the direction of electronic circuit testing, etc., can solve the problems of high use and testing costs for users, inability to detect chip performance status, and insufficient detection or identification accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

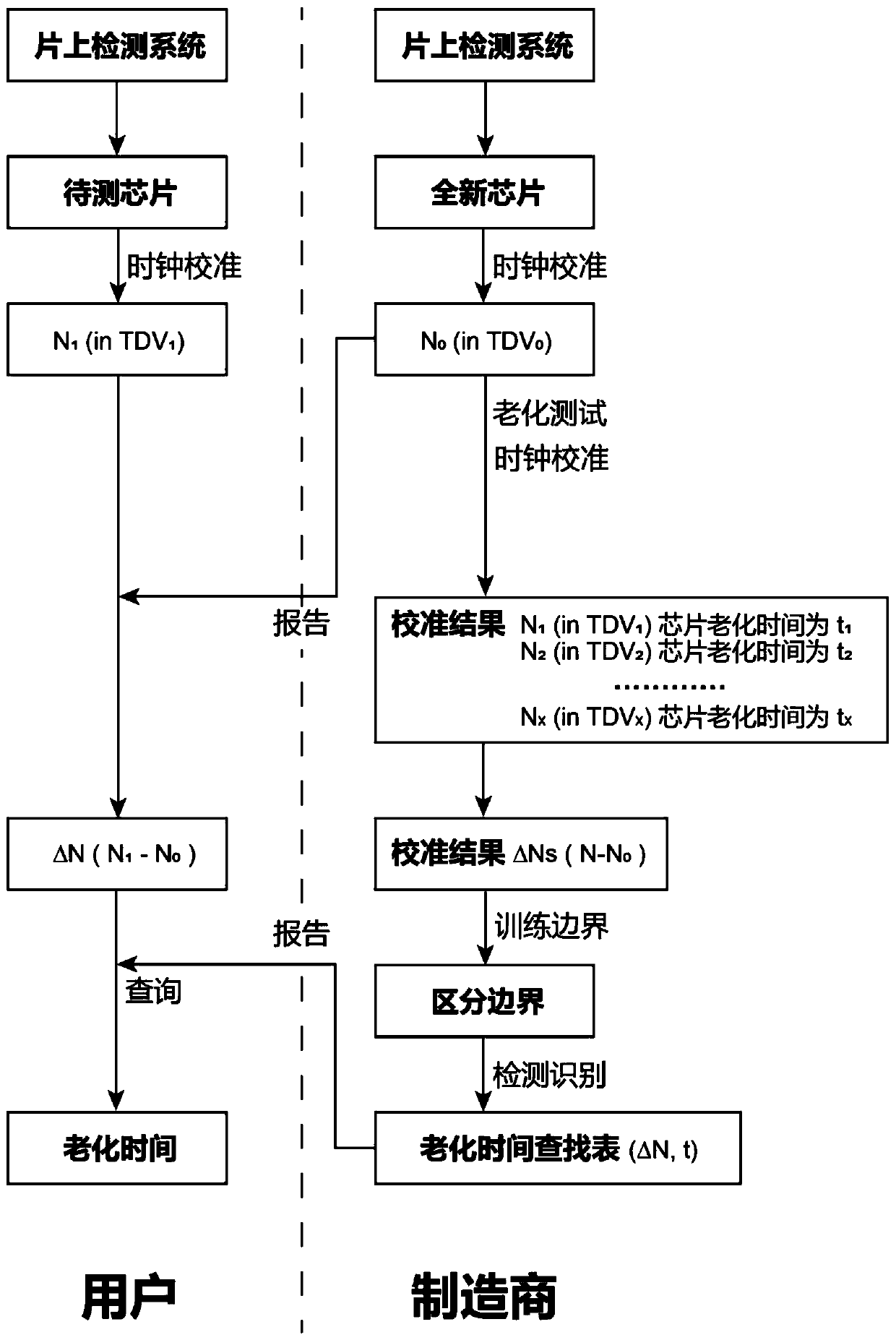

[0029] The following will introduce the specific operation flow and implementation of the burn-in recycling integrated circuit on-chip detection system designed in the present invention with reference to the accompanying drawings.

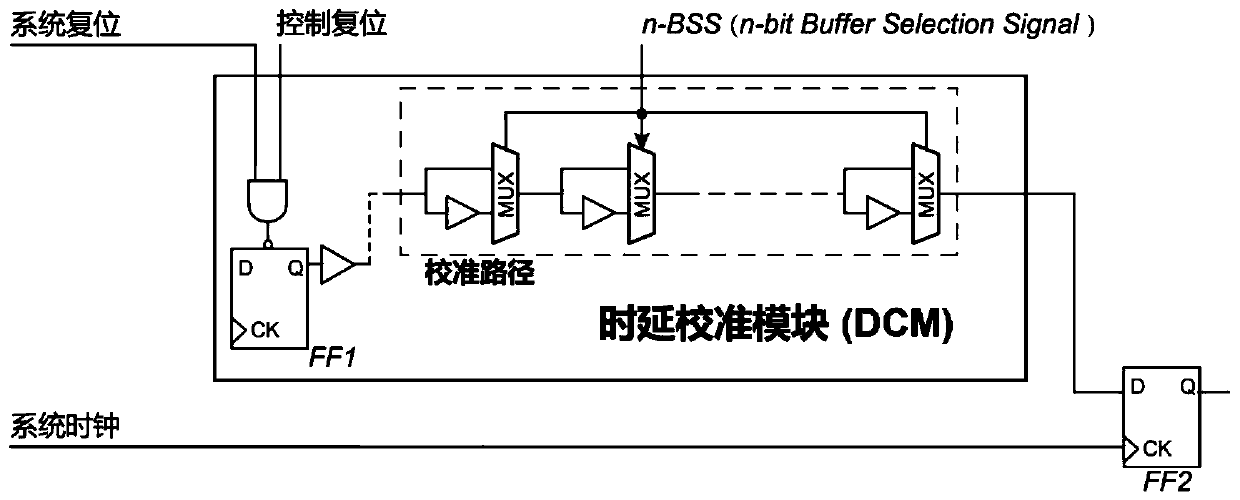

[0030] Step 1: The tester and the user configure the target detection register (hereinafter referred to as TDR) through the JTAG test access port (hereinafter referred to as TAP), and determine the logical value stored in each register in the TDR. The instructions and test data vectors (hereinafter referred to as TDV) inside the TDR are decoded by the control logic of the peripheral control circuit and output the n-level buffer selection signal (hereinafter referred to as n-BSS) to control the number of buffers (Buffer) connected to the calibration path. . Wherein the n-BSS signal will be used in the off-chip detection process of the subsequent step 4.

[0031] Step 2: The delay calibration module not only needs to be calibrated by the clock signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com