A low complexity and fast SIFT feature extraction method based on FPGA

A feature extraction and low-complexity technology, applied in the field of computer vision, can solve the problems of high power consumption, low power consumption, and high speed, and achieve high matching rate, speed improvement, and high stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

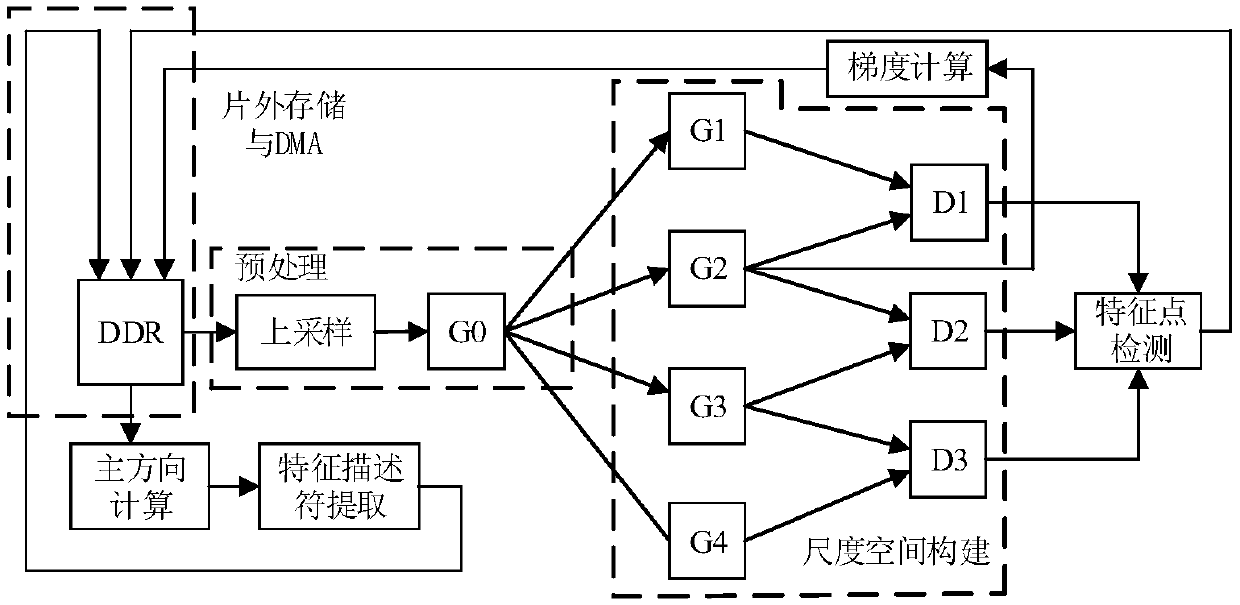

[0023] The proposed SIFT hardware architecture as figure 1 shown. The system mainly includes preprocessing, scale space construction (Gaussian pyramid construction and Gaussian difference pyramid construction), gradient information calculation, feature point detection, feature point main direction calculation and feature descriptor extraction.

[0024] In the preprocessing module, the gray pixels of the original image are transferred to the upsampling module through DMA (direct memory access). The output of the up-sampling module is sent to the initial two-dimensional Gaussian filter module G0 to generate a reference Gaussian image, and then four parallel two-dimensional Gaussian filters G1-G4 are used to generate a four-layer Gaussian image to form a Gaussian pyramid. Gaussian difference images D1 to D3 obtained by subtracting two adjacent layers of Gaussian images form a Gaussian difference pyramid. The detection of feature points is carried out in the difference of Gaussi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com