Design method for cathode short MOS-controlled thyristor layout

A layout design, thyristor technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of burnt devices, enhanced gate signal delay effect, heat accumulation, etc., to shorten the time difference of latch, uniform current distribution, reduce The effect of heat accumulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

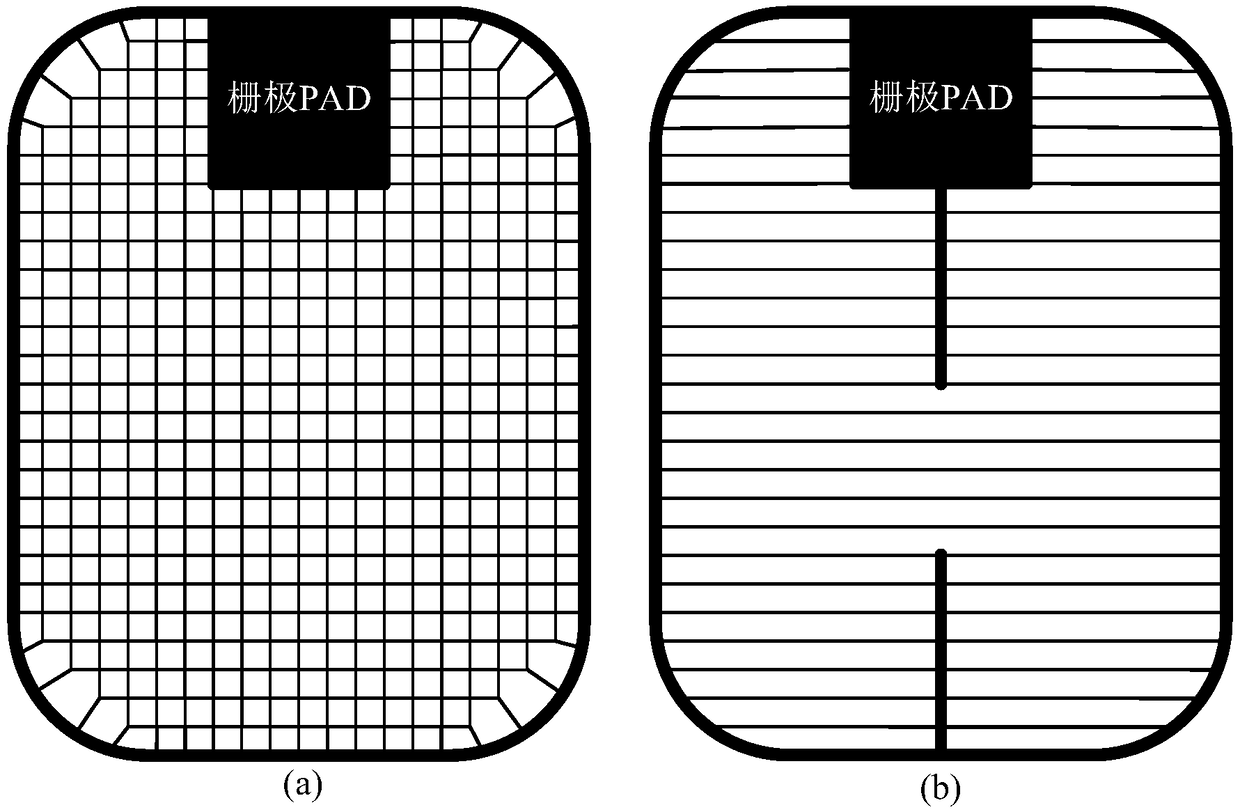

Method used

Image

Examples

Embodiment

[0029] Taking a device with a cell width of 50 μm as an example, the withstand voltage is 1700V. Figure 4Schematic diagram of the topological circuit for the CS-MCT device under transient simulation. Among them, the device works in the RLC loop, the capacitance C is 0.72μF, the charge is 1100V, the inductance L A and L C Both are 20nH, R gex is 5Ω, the gate voltage is 10V, change R gin The value of the gate parasitic resistance at the time of failure is used as the benchmark for normalization processing, and the discharge situation of the CS-MCT device under the high current pulse is obtained. Taking this as an example, it is intuitively shown that the layout design of the present invention is different from the conventional CS-MCT device. The layout design of MCT has the performance advantage in this application field.

[0030] Compared Figure 5 with Image 6 In the figure, the distribution of the anode current in the internal cell and the edge cell during the pulse d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com