A weakly physically non-clonable function circuit utilizing PMOS process deviations

A technology of process deviation and functional circuit, which is applied in the field of weak physical non-clonable functional circuit, can solve the problems that MOS tube cannot adopt the minimum process size, the area of weak PUF circuit is large, and the key cannot be reset, so as to achieve compact layout area and low power consumption. Low, simple structure effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

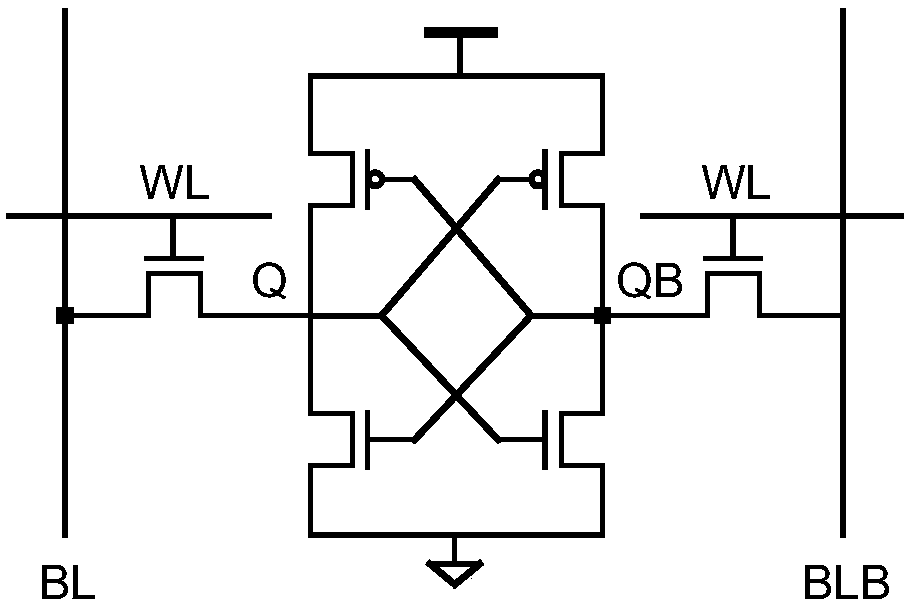

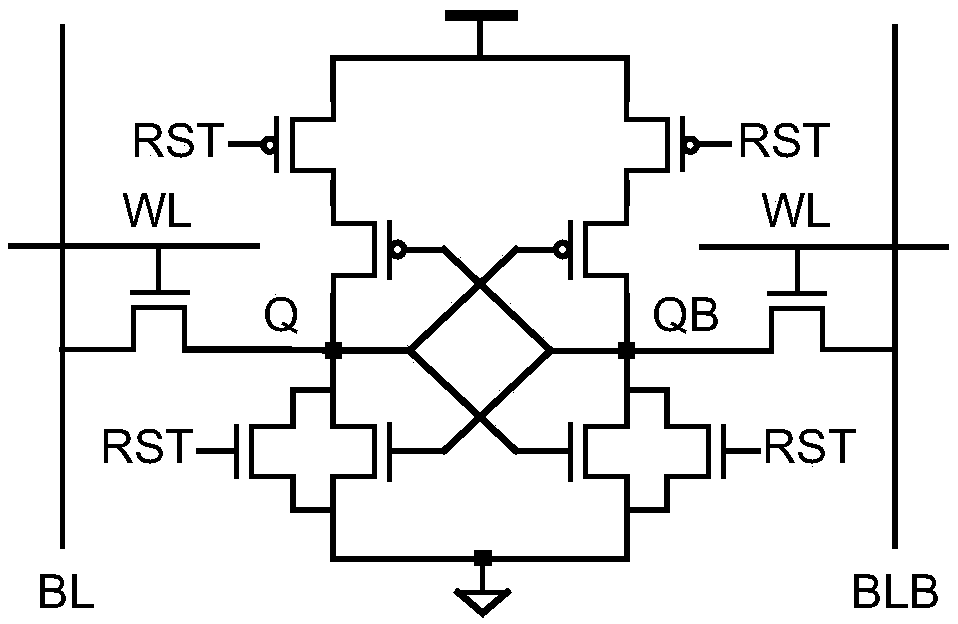

[0023] Example one: such as figure 2 , image 3 with Figure 4 As shown, a weak physical unclonable function circuit using PMOS process deviation includes a decoding circuit, a timing control circuit, a PUF unit array and n shared pin circuits with the same structure. The PUF unit array consists of m×n The PUF unit is arranged in m rows and n columns, and × is the symbol of multiplication operation. The decoding circuit has w-bit input, m-bit output, controlled clock signal input and word line control signal input, and timing control circuit It has an enable signal input terminal, a clock signal input terminal, a pre-discharge signal output terminal, a controlled clock signal output terminal, and a word line control signal output terminal. Each shared pin circuit has a pre-discharge signal input terminal, an output terminal, and a first Bit line connection end, second bit line connection end, each PUF unit has a word line connection end, a first bit line connection end and a sec...

Embodiment 2

[0026] The second embodiment: this embodiment is basically the same as the first embodiment, the difference lies in:

[0027] In this embodiment, such as Figure 5 As shown, the timing control circuit includes a latch LH1, a first two-input AND gate A1, a delay chain, a second two-input AND gate A2, and a buffer BF1; the latch LH1 has a clock terminal, an input terminal and an output terminal, The first two-input AND gate A1 and the second two-input AND gate A2 have a first input terminal, a second input terminal and an output terminal respectively. The input terminal of the latch LH1 is the enable signal input terminal of the timing control circuit. The clock terminal of the LH1 is connected to the second input terminal of the first two-input AND gate A1 and its connection terminal is the clock signal input terminal of the timing control circuit, the output terminal of the latch LH1 and the first two-input AND gate A1 One input is connected, the first two input and the output of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com