Self-calibrated 12 bit SAR ADC structure and self-calibration method thereof

A self-calibration, capacitor array technology, used in analog/digital conversion calibration/testing, electrical components, code conversion, etc., can solve the problems of analog-to-digital conversion offset and low conversion accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

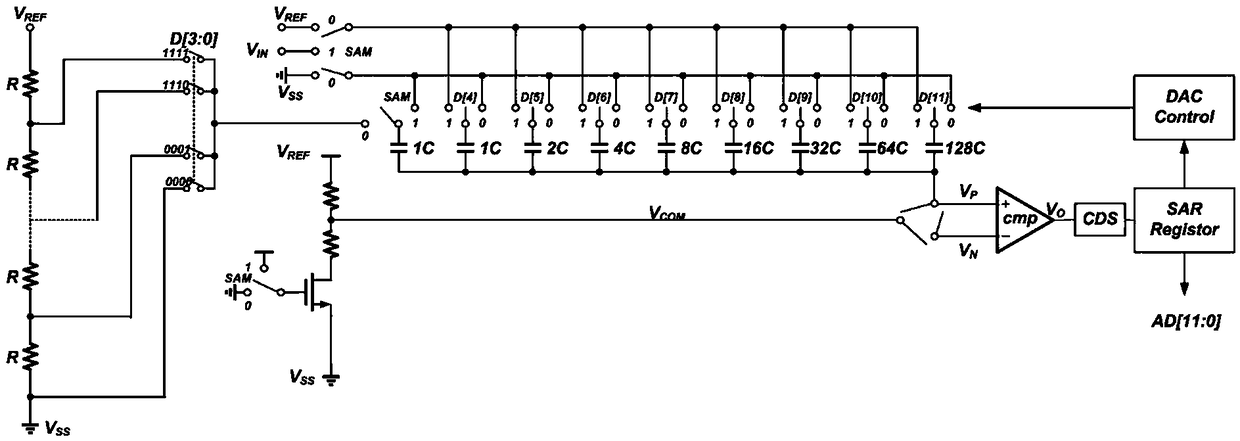

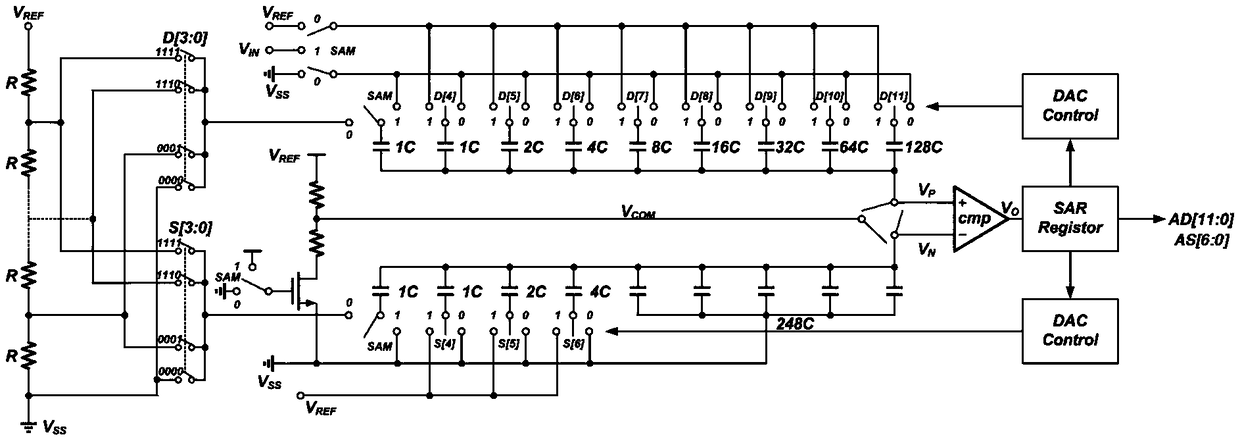

[0029] The present invention provides a self-calibrating 12bit SAR ADC structure, the structure is as follows figure 2 shown. It adopts RC hybrid structure, the high 8 bits are composed of binary weighted capacitors, and the low 4 bits are composed of resistor strings. The self-calibrating 12bit SAR ADC structure includes a self-calibrating capacitor array, a selection switch S[6:0], a comparator CMP, a voltage dividing resistor string, a register SAR Registor and two logic control modules DAC Control, and also includes ADC conversion Capacitor array, selection switch D[11:0]; among them, selection switch S[6:0] refers to selection switch S[6], S[5]..., S[1], S[0], selection Switches D[11:0] refer to selection switches D[0], D[1], D[2], . . . , D[11]. The voltage dividing resistor string is 16 equivalent resistors R connected in series, and the two ends of which are respectively connected to the input voltage V REF and V SS , 16 different kinds of The partial pressure co...

Embodiment 2

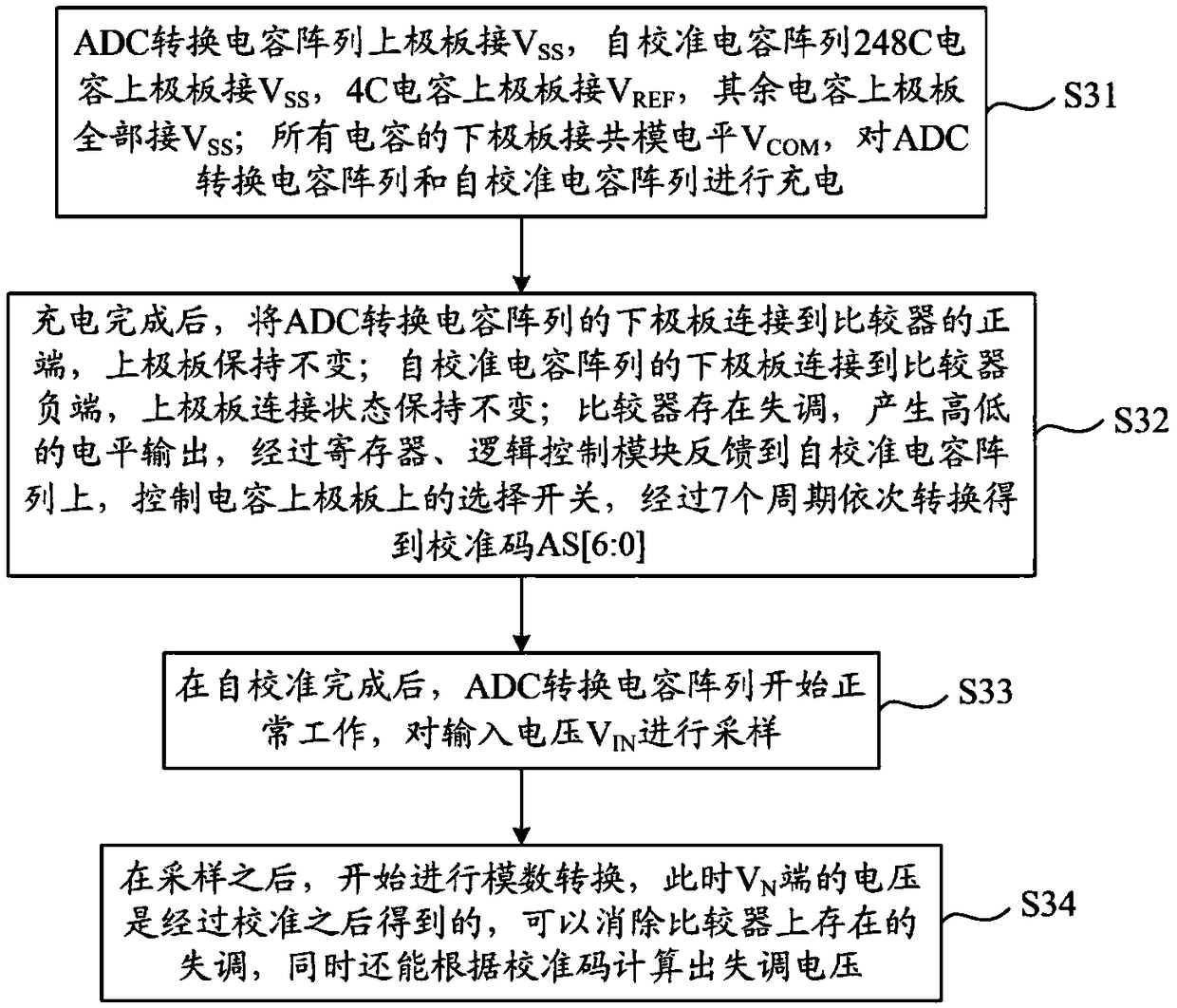

[0034] The present invention provides a self-calibration method of a 12bit SAR ADC structure, the flow chart is as follows image 3 shown. The self-calibration method of described 12bit SAR ADC structure comprises the steps:

[0035] Step S31, the upper plate of the ADC conversion capacitor array is connected to V SS , self-calibration capacitor array 248C capacitor upper plate connected to V SS , the upper plate of the 4C capacitor is connected to V REF , and the upper plates of the remaining capacitors are all connected to V SS ; The lower plates of all capacitors are connected to the common mode level V COM , charge the ADC conversion capacitor array and the self-calibration capacitor array;

[0036] Step S32, after charging is completed, connect the lower plate of the ADC conversion capacitor array to the positive terminal of the comparator, and keep the upper plate unchanged; connect the lower plate of the self-calibration capacitor array to the negative terminal of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com