Design method for heterogeneous reconfigurable diagram calculation accelerator system on the basis of FPGA (Field Programmable Gate Array)

A design method and accelerator technology, applied in computer-aided design, CAD circuit design, calculation, etc., can solve the problems of low software level, low effective calculation rate, low utilization rate of off-chip bandwidth, etc., to achieve low power consumption, acceleration The effect of graph algorithms

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0055] FPGA in the embodiment of the present invention refers to Field Programmable Gate Arrays (Field Programmable GateArrays), and the system designed in the present invention is a heterogeneous system based on PC-FPGA, wherein, the data path between PC and FPGA can adopt PCI-E bus protocol. The data path inside the FPGA on-chip accelerator is illustrated by using the AXI bus protocol as an example to illustrate the data path in the drawings of the embodiments of the present invention, but the present invention is not limited thereto.

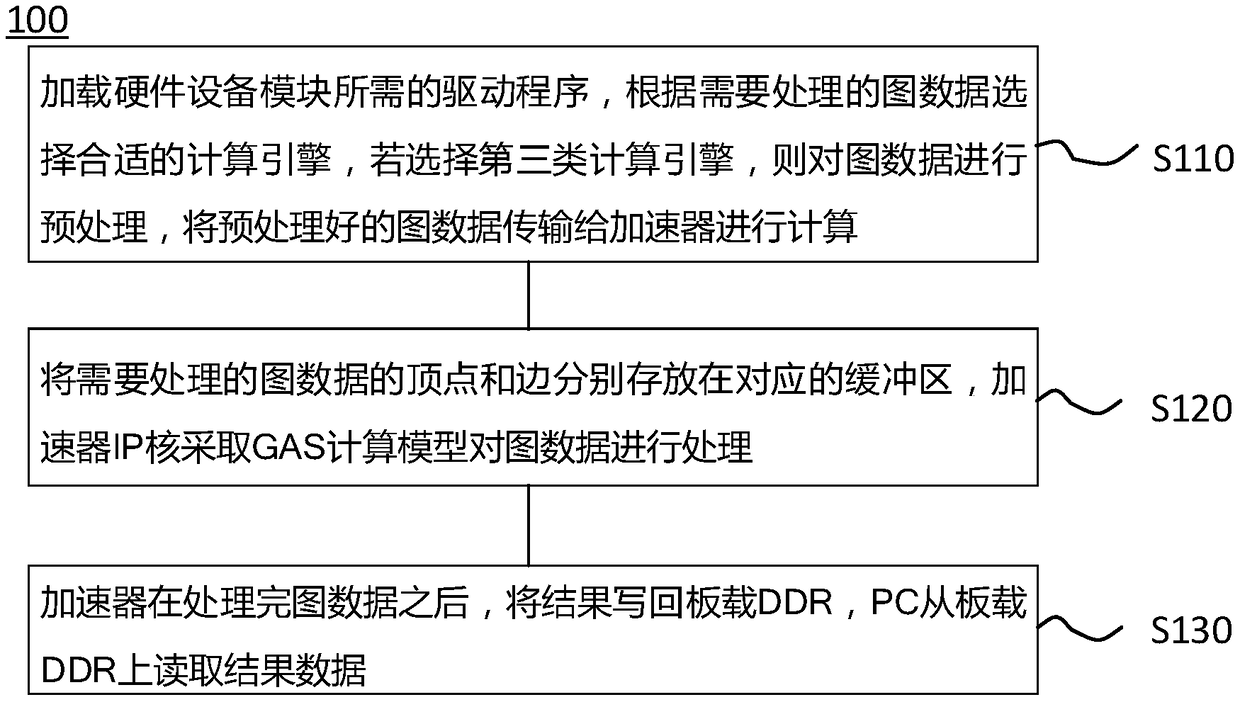

[0056] figure 1 It is a flowchart of an FPGA-based graph computing accelerator design method 100 according to an embodiment of the present invention. The method 100 includes:

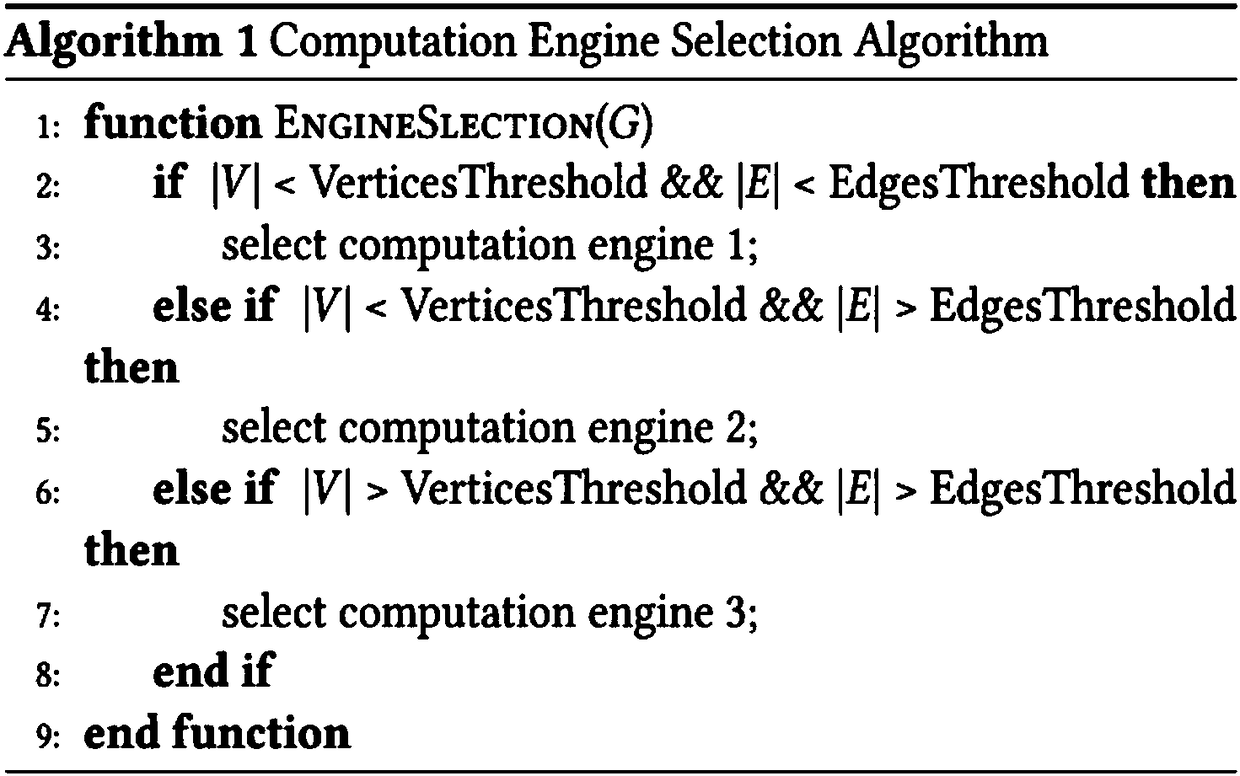

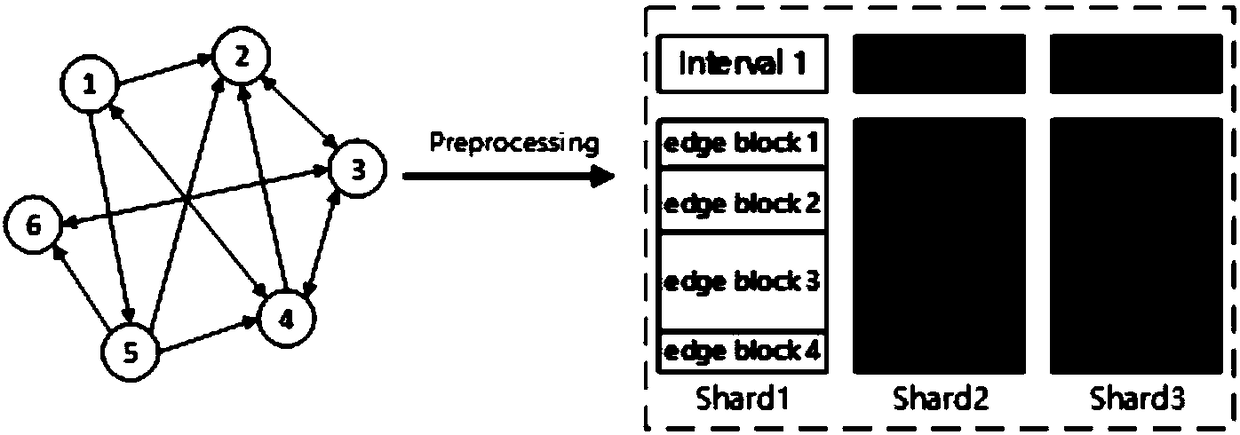

[0057] S110, load the driver program required by the hardware device module, select a suitable computing engine according to the graph data to be processed, if the third type of computing engine is selected, preprocess the graph data, and transmit the preprocessed gr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com