UDP/IP hardware protocol stack based on fpga and its realization method

A protocol and hardware technology, applied in the field of user datagram protocol/network interconnection protocol UDP/IP hardware protocol stack and implementation, can solve the problems of time-consuming data storage operation, different data volume, waste of hardware resources, etc., to save The effect of hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will be further described in detail below with reference to the accompanying drawings.

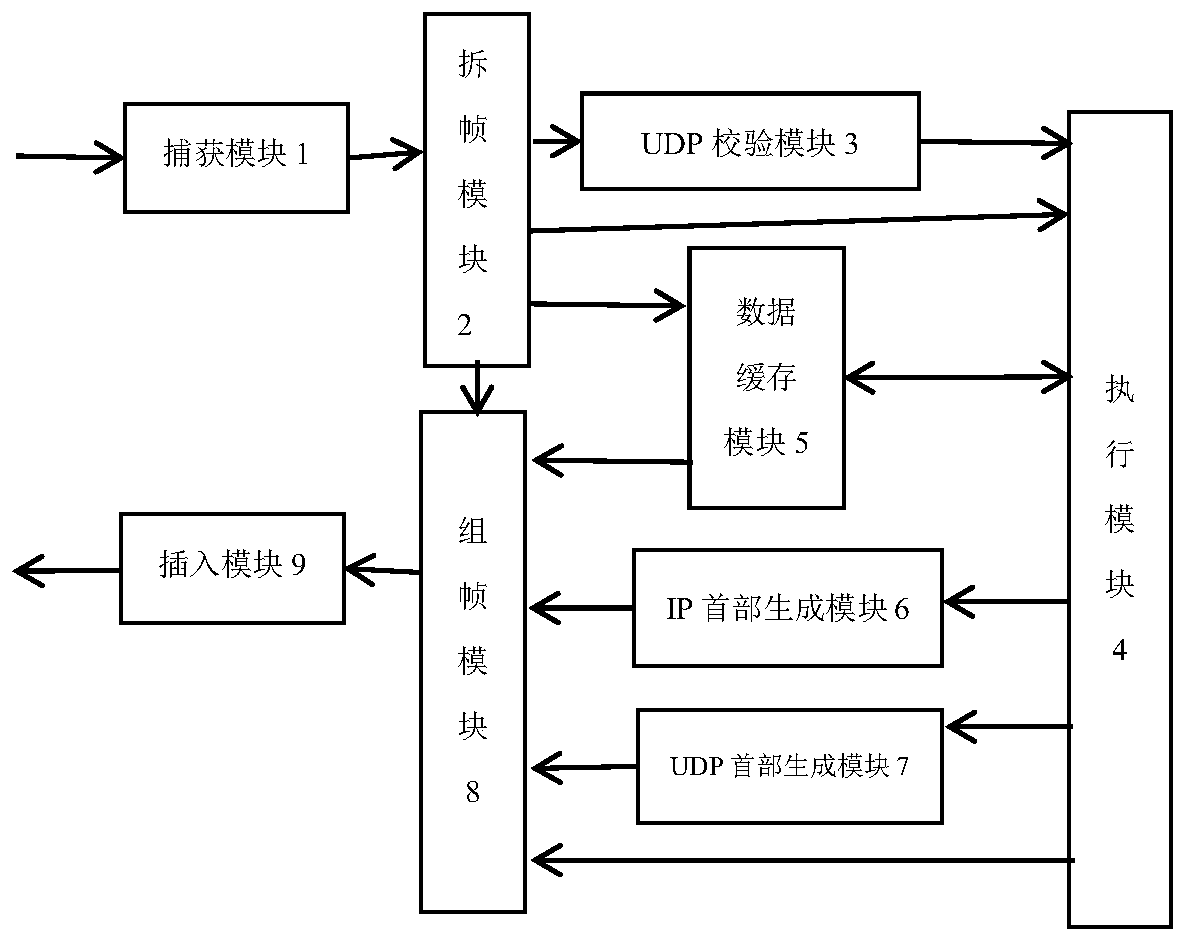

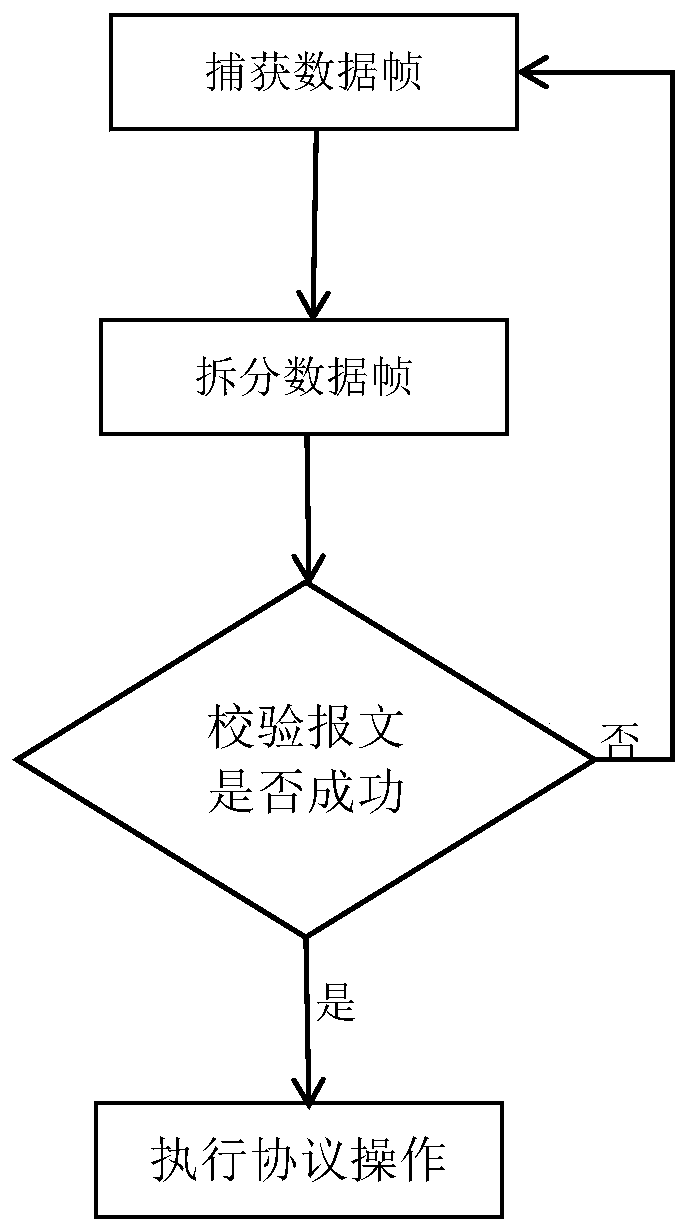

[0038] refer to figure 1 , the device of the present invention includes a capture module 1, a frame removal module 2, a UDP verification module 3, an execution module 4, a data cache module 5, an IP header generation module 6, a UDP header generation module 7, a framing module 8 and an insertion module 9 ;in,

[0039] The transmission of information between the capturing module 1 and the inserting module 9 and between the capturing module 1 and the inserting module 9 is realized through the data FIFO and the corresponding control FIFO.

[0040] The deframing module 2 extracts the control information in the control FIFO received by the capture module 1, extracts the Ethernet frame stored in the data FIFO according to the control information, and sends the extracted Ethernet frame information to the corresponding module. Deframing module 2 extracts the frame in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com