A Synchronous Hybrid Delay Type DPWM Module Based on FPGA

A delay chain, synchronous circuit technology, applied in the direction of pulse duration/width modulation, etc., can solve the problem of limited counter operating frequency delay chain high circuit resource occupancy, difficult to achieve high precision, digital pulse width modulator limited Sampling delay and resolution, etc., to achieve the effect of high production cost, guaranteed accuracy, and high linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

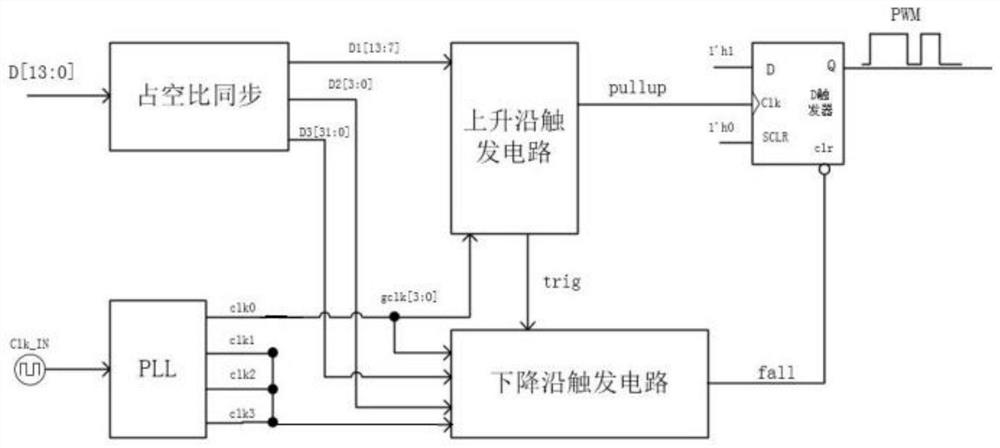

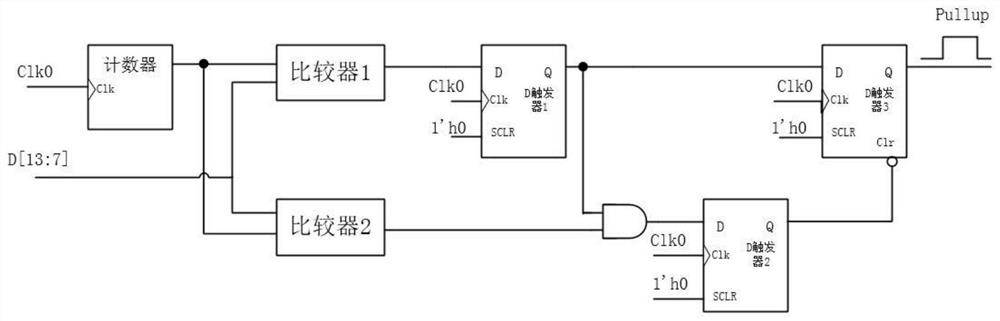

[0032] In this embodiment, the 14-bit DPWM structure is taken as an example (but not limited to 14 bits). An FPGA-based synchronous hybrid delay chain type DPWM module includes: rising edge trigger circuit, falling edge trigger circuit, duty cycle synchronous decoding circuit, register and phase-locked loop clock generation circuit;

[0033] The falling edge trigger circuit includes: two phase shift synchronous circuits, an addition and carry chain reset signal generation circuit;

[0034] The duty cycle synchronous decoding circuit obtains the n-bit duty cycle signal and performs segmentation processing, and converts the n-bit to the m-bit duty cycle signal D in the n-bit duty cycle signal 1 [n-1:m-1] is sent to the rising edge trigger circuit, and the duty cycle signal D from the m-1th to the m-2th bit 2 [m-2:m-3] After decoding, the four-digit digital signal D is obtained 2 [3:0] is sent to the falling edge trigger circuit, and the duty ratio signal D from the m-3 bit to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com