ESD protection circuit based on enhanced PHEMTs

An ESD protection and enhanced technology, applied in the direction of emergency protection circuit devices, emergency protection circuit devices, circuit devices for limiting overcurrent/overvoltage, etc. complex problems, to achieve the effect of low cost, reduced load capacitance, and increased on-voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

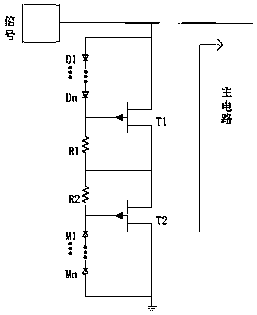

[0031] combine figure 2 , which describes the first specific embodiment of the present invention in detail, but does not limit the claims of the present invention in any way.

[0032] Such as figure 2 As shown, an enhanced PHEMT-based ESD protection circuit includes an ESD bias circuit and a resistor, and also includes two enhanced PHEMT tubes T1 and T2 connected in series, the source of T1 is connected to the source of T2, The drain of the T1 is connected to the chip pad that needs ESD circuit protection, and the drain of the T2 is grounded;

[0033] There are two ESD bias circuits, which are respectively connected between the drain and the gate of the T1 and between the gate and the drain of the T2;

[0034] There are two resistors, namely R1 and R2, the resistor R1 is connected between the gate and the source of the T1, and the resistor R2 is connected between the source and the gate of the T2.

[0035] More specifically, the ESD bias circuit includes several diodes co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com