Method for rapidly positioning short circuit of three-dimensional memory array zone

A memory array and three-dimensional technology, applied in the field of failure analysis, can solve problems affecting product performance, achieve rapid positioning and characterization, and narrow the target range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, but it should be understood that the protection scope of the present invention is not limited by the specific embodiments.

[0016] Unless expressly stated otherwise, throughout the specification and claims, the term "comprise" or variations thereof such as "includes" or "includes" and the like will be understood to include the stated elements or constituents, and not Other elements or other components are not excluded.

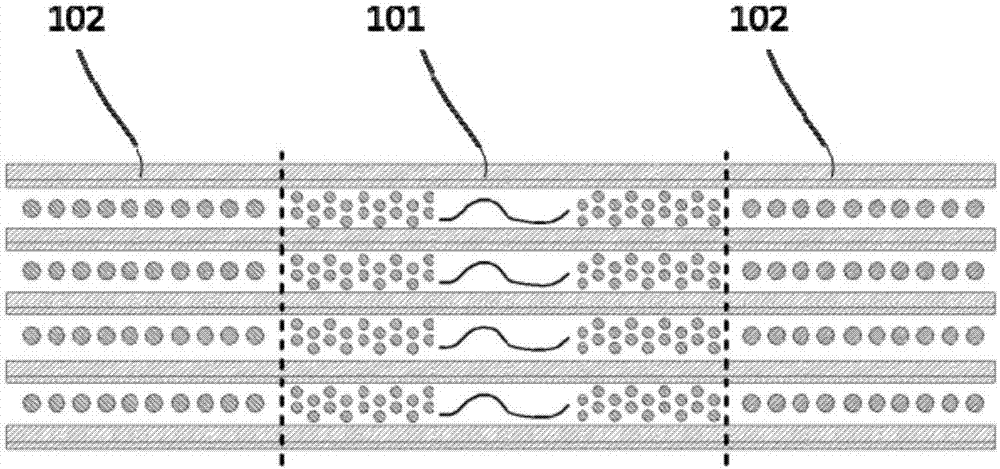

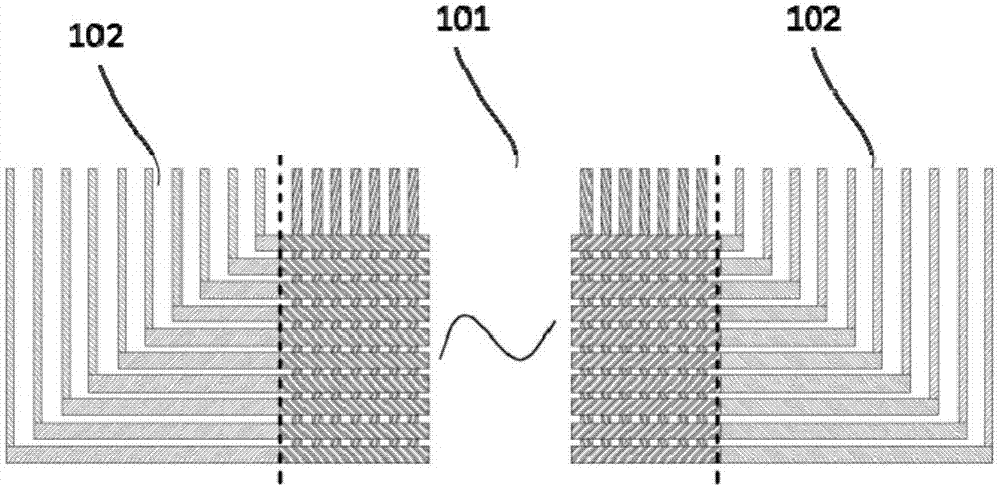

[0017] figure 1 is a top view of a chip according to the invention. The chip of the present invention includes figure 2 is a schematic top view of a chip according to the present invention. image 3 is a schematic cross-sectional view of a chip according to the present invention. It can be seen from the figure that the chip of the present invention includes an array area 101 and a stepped area 102 . There is a short c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com