Coding method of one kind of low-density parity checking codes for deep space application

A technology of low-density parity and coding method, applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc. Implementing complexity and other issues to achieve the effect of reducing hardware resources, reducing complexity, and low complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0034] Below in conjunction with Table 1-Table 3, the schemes in Embodiments 1 and 2 are further introduced, see the following description for details:

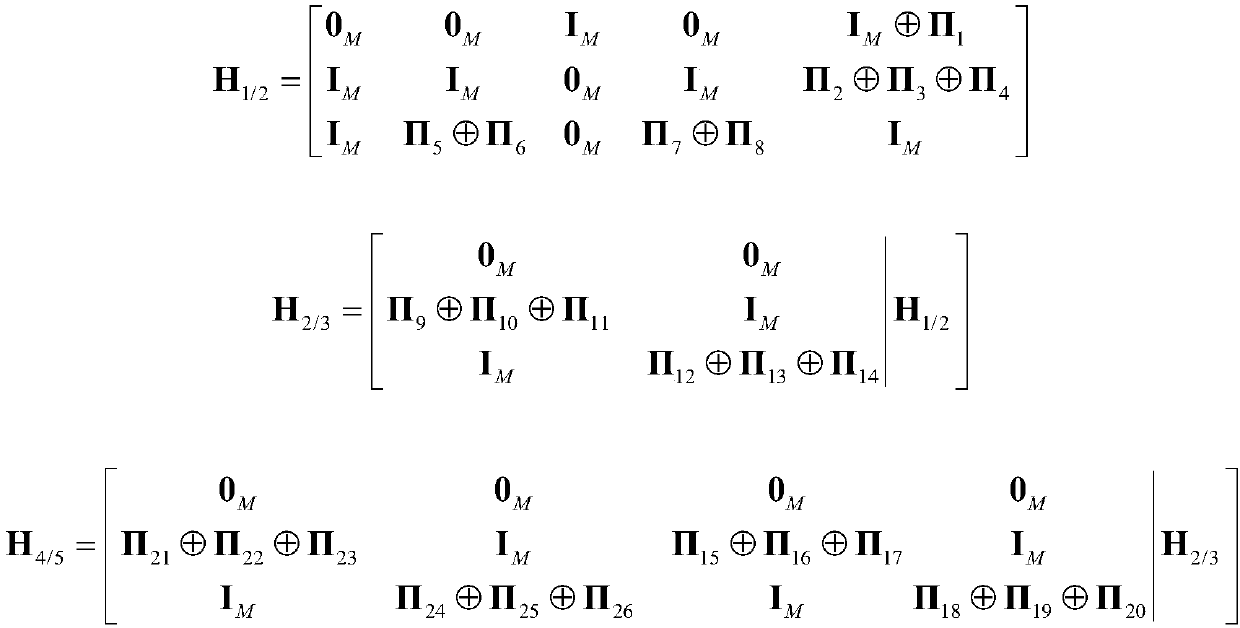

[0035] In the CCSDS standard, the structure of the parity check matrix H of the LDPC code with the code rate r of 1 / 2, 2 / 3 and 4 / 5 is as follows figure 1 shown. Among them, I M Indicates the identity matrix of M×M, 0 M Represents an M×M all-zero matrix, M represents the size of the sub-matrix, and its values are shown in Table 1 under different information code block length k and code rate r.

[0036] Table 1 The value of the size M of the LDPC code submatrix

[0037]

[0038] Π K , K∈{1,2,...,26} represents the M×M permutation matrix, Π K The non-zero elements in the i-th row are located at the π-th K (i) column, where i∈{0,...,M-1}, π K The value of (i) is determined by formula (1):

[0039]

[0040] in, Represents rounding down, mod represents modulo operation, θ K , φ K The value of (j, M) can be seen ...

Embodiment 2

[0060] Taking the LDPC code with a code length of 1024 and a code rate of 1 / 2 as an example, combine Figure 1-Figure 3 Carry out feasibility verification to the scheme in embodiment 1-3, see the following description for details:

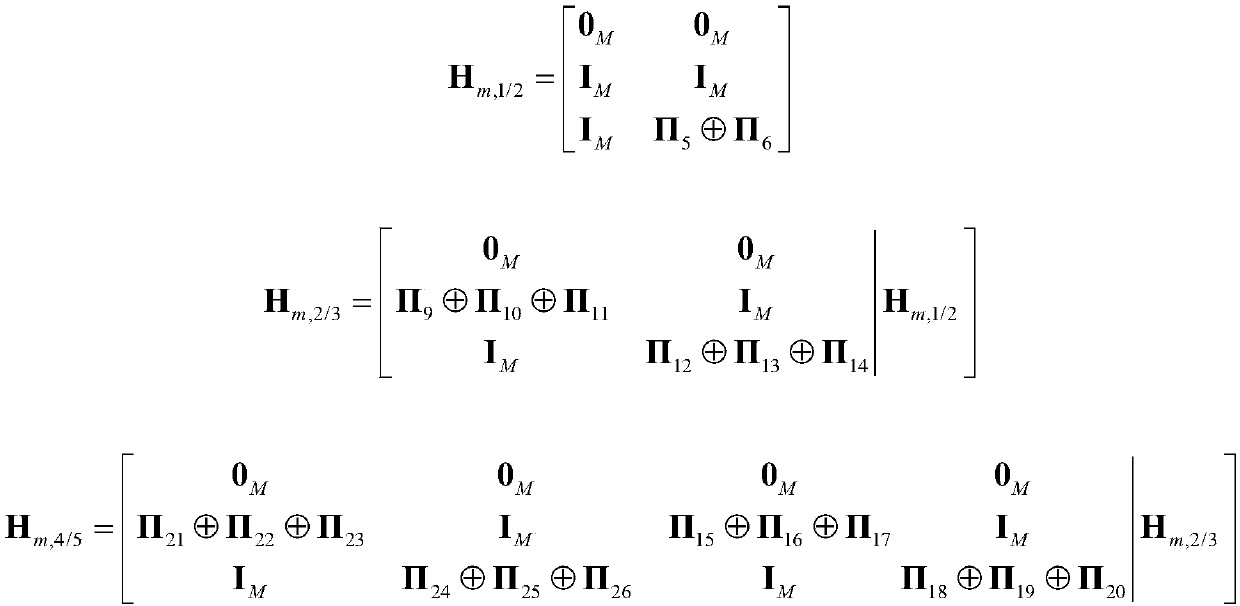

[0061] Step 1: Express the parity check matrix as H=[H m ,H c ] 3M×5M , H m The dimension is 3M×2M, H c The dimension of is 3M×3M, and the sub-matrix size M=512.

[0062] Step 2: Calculate the intermediate vector For LDPC codes with code rate 1 / 2, H m has the following form:

[0063]

[0064] The information bit vector m can be expressed as in and The dimension of is M×1, then there are:

[0065]

[0066]

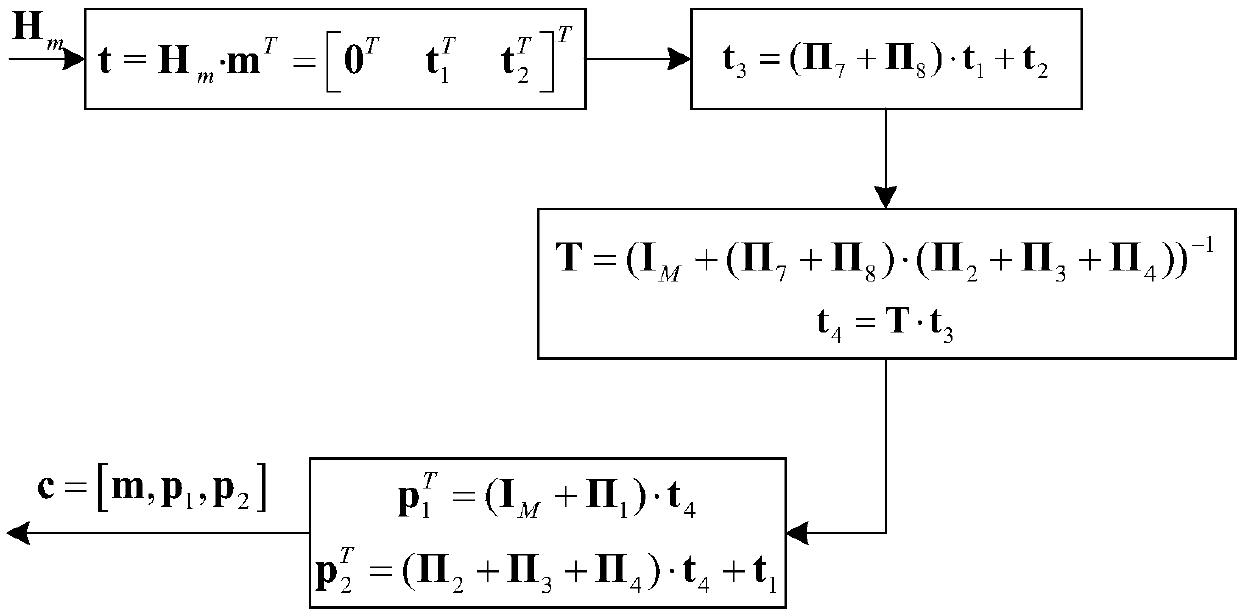

[0067] where the vector t 1 , t 2 The dimension of is M×1, and the circuit realization structure is as follows Figure 4 shown.

[0068] Step 3: The matrix H c Decomposed into four sub-matrices,

[0069] which is in C=[0 M Π 7 +Π 8 ], D=[I M ],

[0070] Construct matrix T=(D+CA -1 B) -1 =(I M +(Π 7 +Π ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com