Bidirectional ESD protection anti-latch-up device of holosymmetric dual-grid-control-diode triggering SCR structure

A gated diode and ESD protection technology, applied in diodes, electro-solid devices, semiconductor devices, etc., can solve the problems of high trigger voltage and low sustain voltage, and achieve the effect of reducing the trigger voltage and improving the turn-on speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Below in conjunction with accompanying drawing and specific embodiment the present invention will be described in further detail:

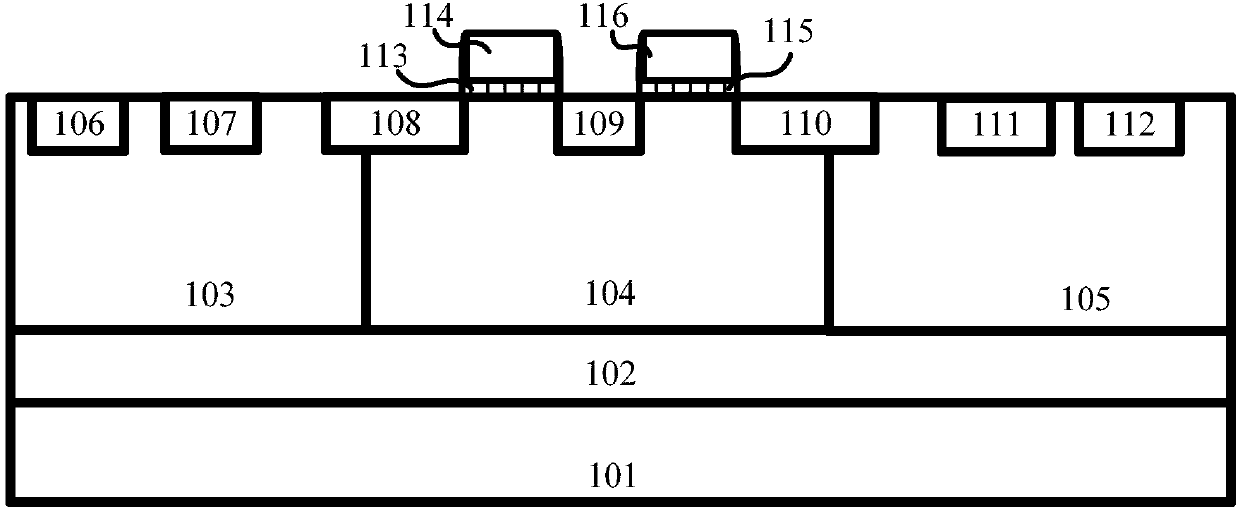

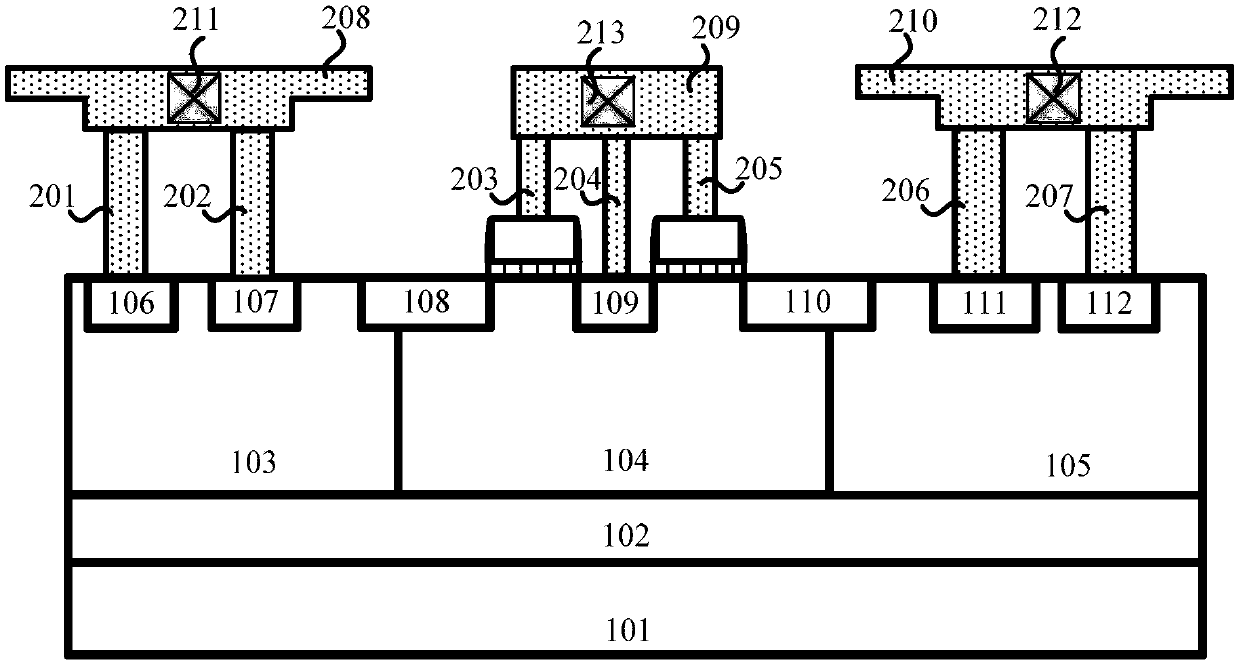

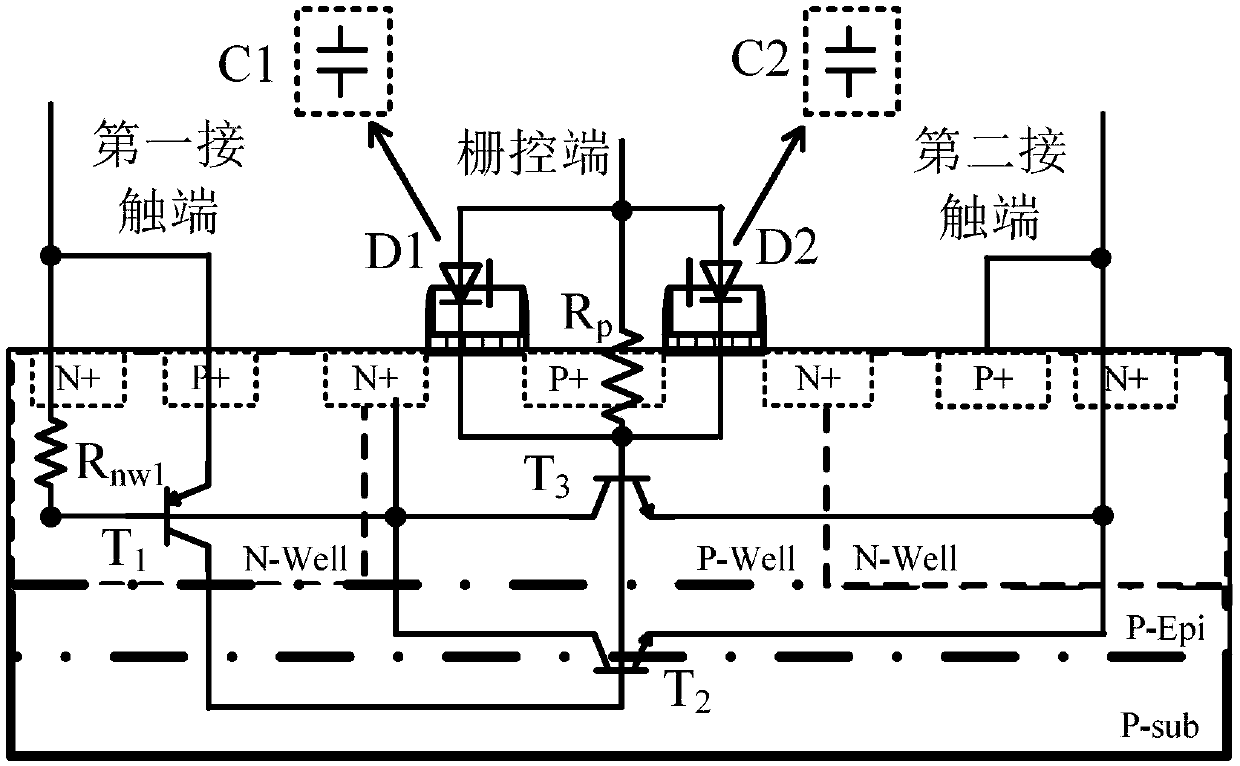

[0028] The example of the present invention designs a bidirectional ESD protection anti-latch-up device with a fully symmetrical double gate-controlled diode triggering SCR structure, making full use of the advantages of low trigger voltage and fast turn-on speed of the resistance-capacitance coupling circuit, combined with the strong ESD robustness of the SCR structure advantages, and by forming multiple current discharge paths to effectively shunt ESD pulses, the designed device can form a resistance-capacitance coupling auxiliary trigger path composed of parasitic P-well resistance and a gate-controlled diode under the action of ESD stress, and a longitudinal bias The high sustain voltage path composed of NPN and parasitic well resistance, also has a fully symmetrical layout structure composed of the first N well, P well and second N well...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com