A method for manufacturing a three-dimensional memory device and its device structure

A technology for three-dimensional storage and manufacturing methods, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of electrical connection failure, distorted photolithography process pattern, contact holes cannot fall on the steps correctly, etc., to reduce Effects of deformation and distortion, increasing effective contact area, reducing contact failure problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

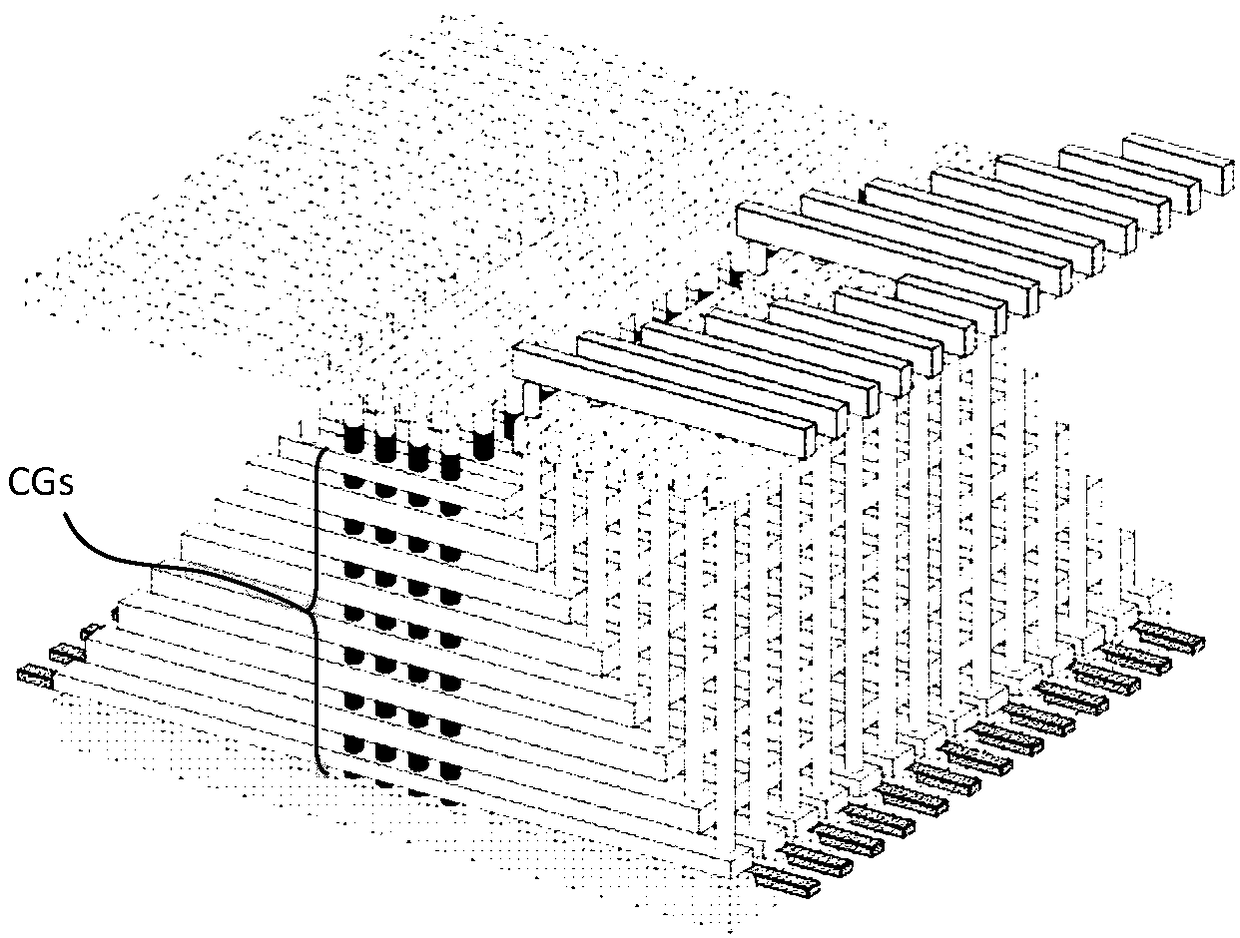

[0055] refer to Figure 8 As shown, Embodiment 1 of the present invention proposes a method for manufacturing a three-dimensional memory device, including the following steps:

[0056] A substrate is provided, on which a three-dimensional memory device area is formed, and the three-dimensional memory device area includes a multi-layer memory stack structure sequentially formed on the substrate;

[0057] forming a core platform area and a plurality of partition pattern areas adjacent to at least one side of the core platform area by forming the stacked structure through lithography and etching processes;

[0058] Each of the plurality of partitioned pattern areas is formed as a trapezoidal three-dimensional structure 1, and at a cross-section in a direction parallel to the side of the core platform area and perpendicular to the surface of the substrate, a base is longer than The isosceles trapezoid of the top side, and, from the section 11 closest to the core platform area to ...

Embodiment 2

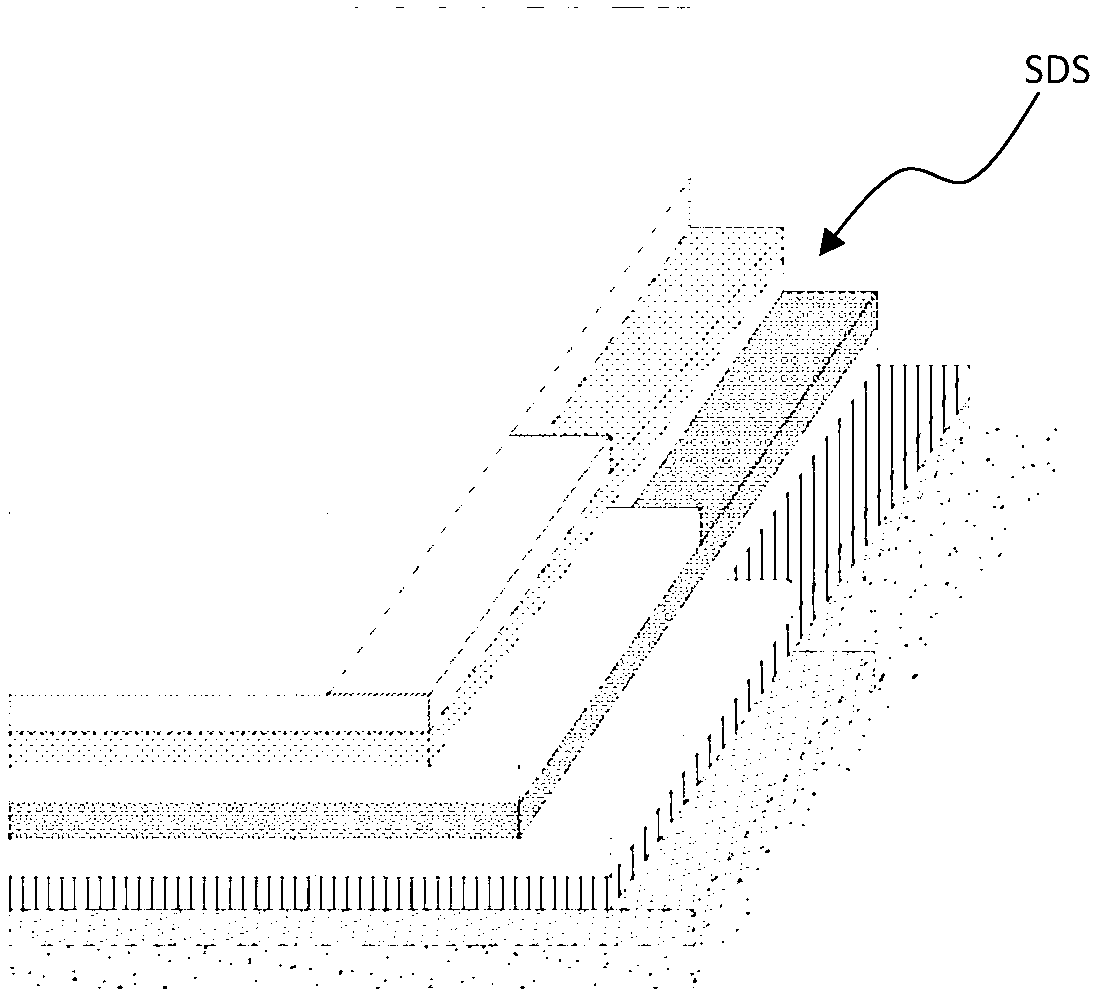

[0061] refer to Figure 9 As shown, Embodiment 2 of the present invention proposes a method for manufacturing a three-dimensional memory device, including the following steps:

[0062] A substrate is provided, on which a three-dimensional memory device area is formed, and the three-dimensional memory device area includes a multi-layer memory stack structure sequentially formed on the substrate;

[0063] forming a core platform area and a plurality of partition pattern areas adjacent to at least one side of the core platform area by forming the stacked structure through lithography and etching processes;

[0064] Each of the plurality of partitioned graphics areas 2 includes: a first rectangular area 21 located on the side away from the core platform area, a second rectangular area 22 close to the side of the core platform area, and An isosceles trapezoidal area 23 located between the first rectangular area 21 and the second rectangular area 22, wherein the long side length of...

Embodiment 3

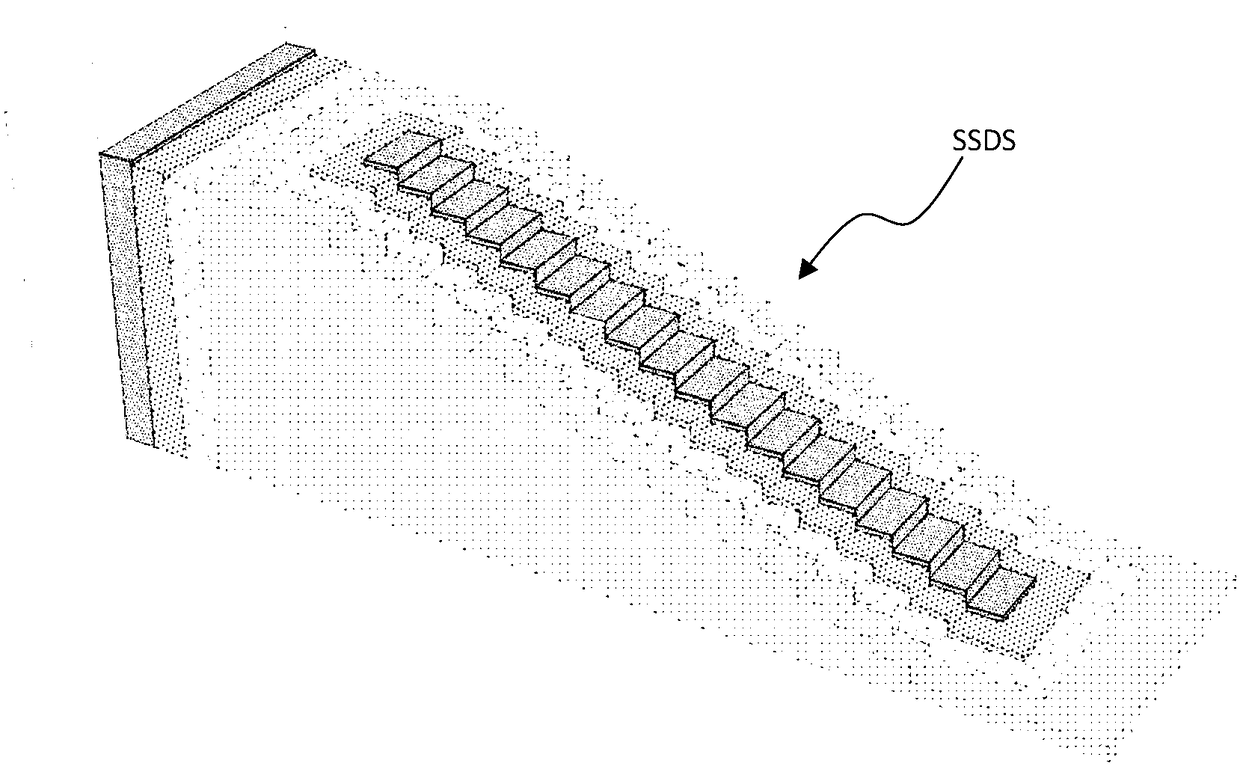

[0067] The third embodiment is a further improvement on the second embodiment above, and the same parts as the second embodiment will not be repeated.

[0068] Such as Figure 10 As shown, the isosceles trapezoidal area 23 is composed of a plurality of sub-rectangular areas 231 of different lengths, and the length of each of the sub-rectangular areas 231 is from the second rectangular area 22 to the first rectangular area 21 The direction of is gradually reduced, and the length relationship between every two adjacent sub-rectangular areas 231 is:

[0069] b=a+2*TKss / n,

[0070] Wherein: b is the length of the sub-rectangular area closer to the second rectangular area in the two adjacent sub-rectangular areas, a is the length of the sub-rectangular area closer to the first rectangular area in the two adjacent sub-rectangular areas, and TKss is the described The total height of the step structure, n is the number of steps of the step structure, wherein the value range of n is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com