A short-pulse d flip-flop based on finfet device

A short pulse and trigger technology, applied in the direction of pulse technology, pulse generation, electric pulse generation, etc., can solve the problems of large number of FinFET tubes, short signal width, high power consumption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

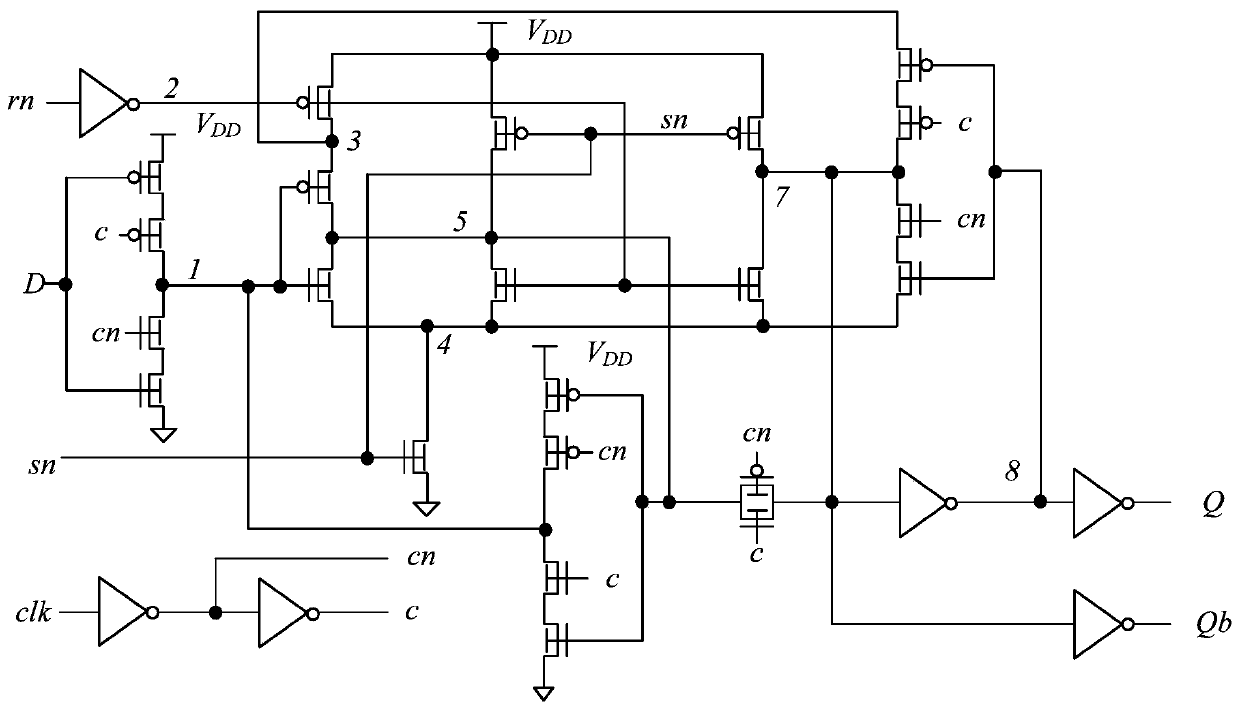

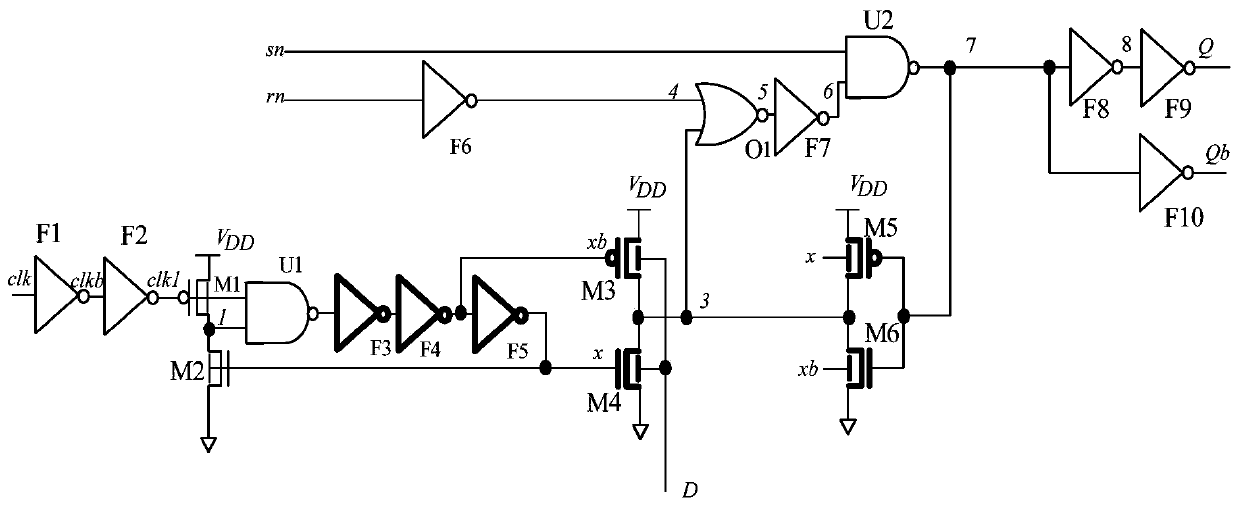

[0030] Embodiment one: if figure 2 As shown, a short-pulse D flip-flop based on FinFET devices includes a first FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, a fourth FinFET tube M4, a fifth FinFET tube M5, and a sixth FinFET tube Tube M6, first inverter F1, second inverter F2, third inverter F3, fourth inverter F4, fifth inverter F5, sixth inverter F6, seventh inverter F7, the eighth inverter F8, the ninth inverter F9, the tenth inverter F10, the first two-input NOR gate O1, the first two-input NAND gate U1 and the second two-input NAND gate U2; The first two-input NOR gate O1, the first two-input NOR gate O1 and the second two-input NAND gate U2 respectively have a first input terminal, a second input terminal and an output terminal; the first FinFET tube M1, the third FinFET The tube M3 and the fifth FinFET tube M5 are all P-type FinFET tubes, the second FinFET tube M2, the fourth FinFET tube M4 and the sixth FinFET tube M6 are all N-type FinFET tubes, ...

Embodiment 2

[0031] Embodiment two: if figure 2As shown, a short-pulse D flip-flop based on FinFET devices includes a first FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, a fourth FinFET tube M4, a fifth FinFET tube M5, and a sixth FinFET tube Tube M6, first inverter F1, second inverter F2, third inverter F3, fourth inverter F4, fifth inverter F5, sixth inverter F6, seventh inverter F7, the eighth inverter F8, the ninth inverter F9, the tenth inverter F10, the first two-input NOR gate O1, the first two-input NAND gate U1 and the second two-input NAND gate U2; The first two-input NOR gate O1, the first two-input NOR gate O1 and the second two-input NAND gate U2 respectively have a first input terminal, a second input terminal and an output terminal; the first FinFET tube M1, the third FinFET The tube M3 and the fifth FinFET tube M5 are all P-type FinFET tubes, the second FinFET tube M2, the fourth FinFET tube M4 and the sixth FinFET tube M6 are all N-type FinFET tubes, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com