Chip embedded silicon substrate type fan-out type packaging structure and manufacturing method therefor

A packaging structure, fan-out technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve silicon substrate etching cost and process difficulty, etching silicon substrate uniformity difficulty, crystal Large round warpage and other problems, to achieve the effect of reducing etching and packaging costs, reducing packaging costs, and reducing warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

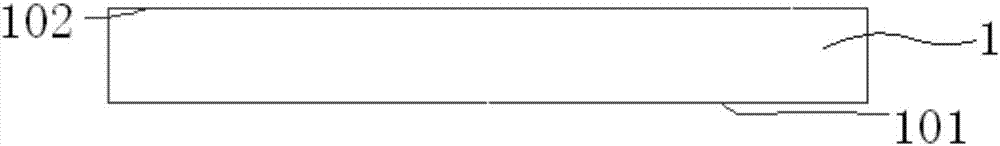

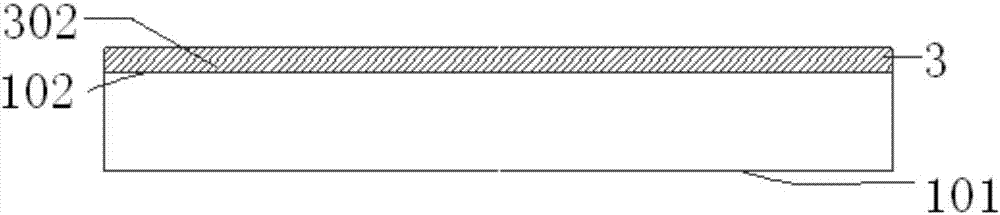

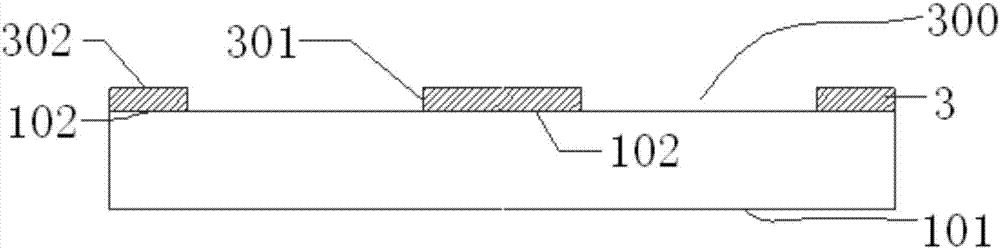

[0052] Such as Figure 1.1-Figure 1.10 Shown is a cross-sectional view of a chip-embedded fan-out package structure according to an embodiment of the present invention. The packaging structure in this embodiment 1 includes a silicon substrate 1, the silicon substrate 1 has a first surface 102 and a second surface 101 opposite to it, and at least one Groove A103 that two surfaces extend, and this groove A103 depth is relatively shallow, that is to say the bonding pad surface of the chip that places in it will be higher than the first surface of silicon substrate a certain distance, and this groove A is preferably straight groove or The angle between the side wall and the bottom surface is 80 to 120°. The structure diagram of this embodiment is a straight groove shape; the first surface of the silicon substrate is laid with a thick glue layer 3, that is, the thick glue layer 3 is located on the first surface of the silicon substrate. On a surface 102, the upper surface 302 of t...

Embodiment 2

[0093] Such as Figure 2.1-Figure 2.11 As shown, as shown in the cross-sectional view of a chip-embedded fan-out package structure according to another embodiment of the present invention, Embodiment 2 of the present invention basically includes the technical features of Embodiment 1, and the difference is that the thick adhesive layer is No photoresist, and the thick glue layer covers the side of the chip and fills the gap between the side of the chip and the groove A; the thick glue layer and the pad surface of the chip are laid with A dielectric layer, on which a metal wiring layer, a passivation layer, and conductive bumps are sequentially arranged, and at least part of the conductive bumps fan out above the thick adhesive layer, and the metal wiring layer passes through the dielectric layer The opening formed on the passivation layer is electrically connected to the pad of the chip, and the conductive bump is electrically connected to the metal wiring layer through the op...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com