Anti-emi super junction vdmos device structure and its preparation method

A device structure, deep trench technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as high doping concentration, serious EMI problems, and EMI at the input and output ends of the circuit system , to achieve the effect of improving the EMI problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be described in detail below in combination with specific embodiments.

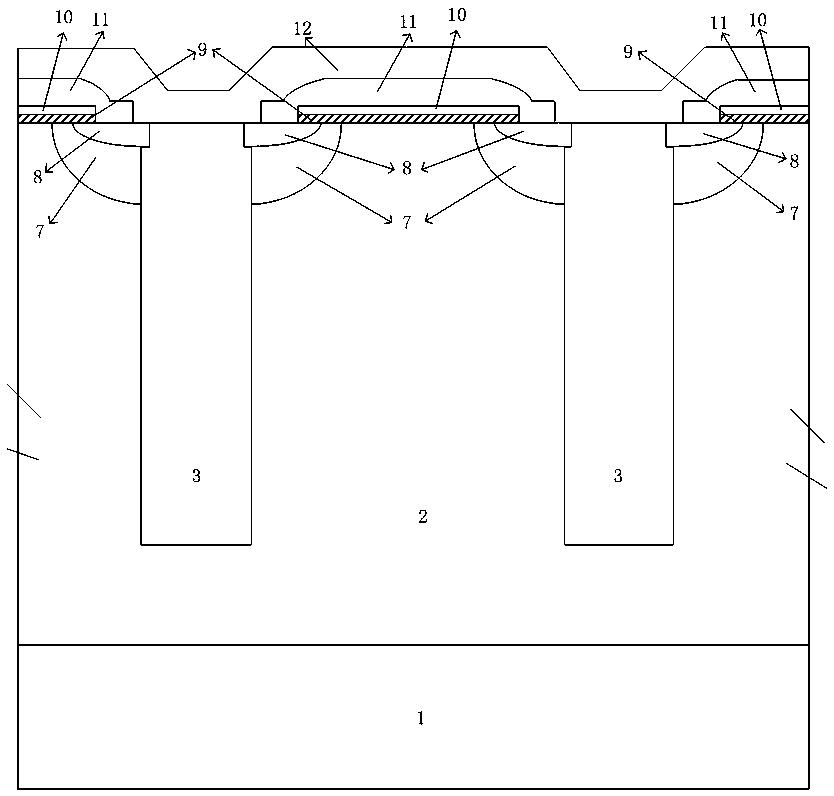

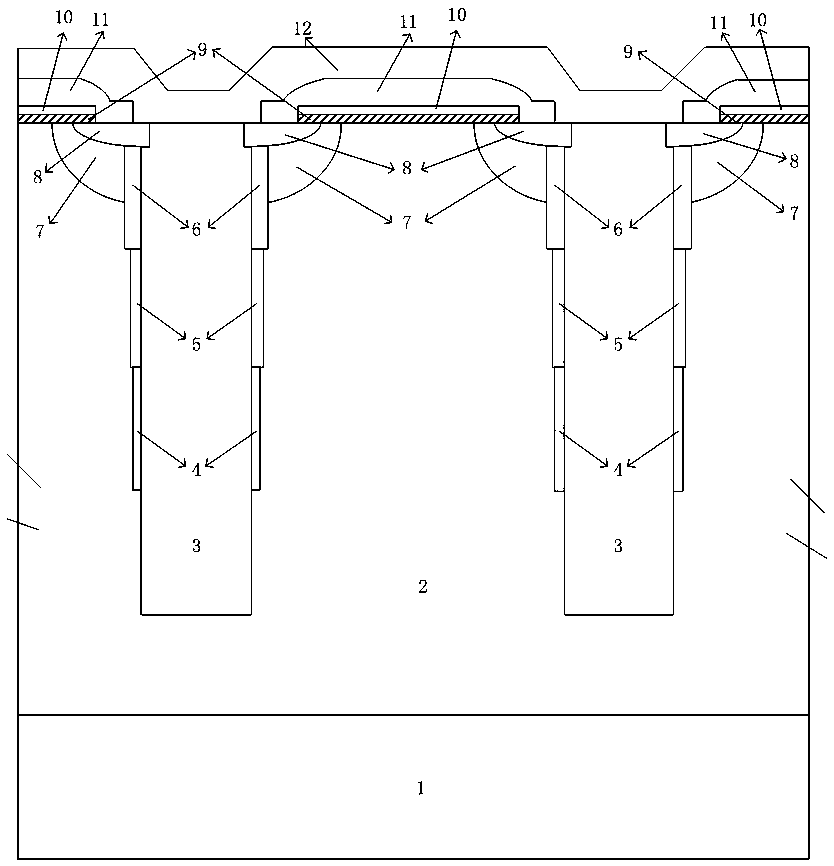

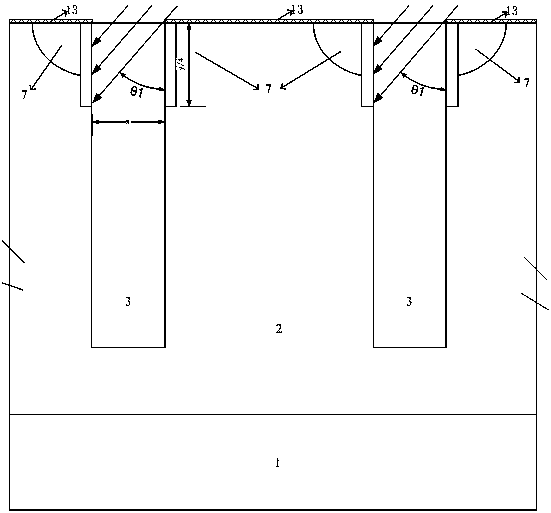

[0033] The invention relates to a method for manufacturing an EMI-resistant superjunction VDMOS device. In the process of manufacturing superjunction using deep trench epitaxial filling technology, after etching the deep trench, three times of boron ion implantation with different inclination angles are used in sequence. A P-type auxiliary depletion first region 6 , a P-type auxiliary depletion second region 5 and a P-type auxiliary depletion third region 4 are formed. Specifically, it is realized through the following steps:

[0034] Step 1. Using the epitaxial process, the heavily doped N + An N-type epitaxial layer 2 of 35-50 μm is epitaxially grown on the substrate 1;

[0035] Step 2: Perform boron ion implantation on the N-type epitaxial layer 2 through the Pbody photolithography mask, and push the junction at a high temperature of 900-1200°C for 90-300 minutes to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com